# Topical Workshop on Electronics for Particle Physics

Aix-la Chapelle September 20-24<sup>th</sup> 2010

LPNHE Paris, October 2010

Jean-Francois Genat

http://indico.cern.ch/...

# Program

### **Plenary talks**

| HEP in Germany                                                | Be |

|---------------------------------------------------------------|----|

| Advanced Electronics for HEP and beyond                       | Ka |

| HEP at Aachen                                                 | Lu |

| Electronics for FEL, a high rate camera                       | Pe |

| LHC Status and Plans                                          | Ra |

| ASICs and FPGA at ESA                                         | Ro |

| 3D MPW runs for HEP                                           | Kł |

| Optical Technologies for Data Communications                  | Fr |

| New interconnect technologies                                 | Pi |

| Preparation for heavy ions at ALICE and other LHC experiments | A  |

| Obsolescence issues for the LHC Electronics                   | Vi |

| Physics for pedestrians                                       | Pa |

|                                                               |    |

### Working Groups

Power Microelectronics Users Group Opto Working Groups xTCA Bernhard Spaan Karlheinz Meier Lutz Feld Peter Goettlicher Ralph Assmann Roland Weigand Kholdoun Torki Francois Vasey Piet de Moor Andrea Dainese Vincent Spellane Patrick Puzo (TU Dortmund) (U Heidelberg) (U Aachen) (DESY) (CERN) (ESA) (CMP Grenoble) (CERN) (IMEC) (INFN Padova) (Lockeed Martin) (LAL Orsay)

Philippe Farthouat Kostas Kloukinas K.K. Gan Magnus Hansen

(CERN) (CERN) (Ohio state U) (CERN)

# Program

### **Parallel Sessions**

ASICs (Three sessions) Opto and Links Power, Grounding & Shielding Data Acquisition, xTCA Packaging and Interconnect Triggers FPGA Radiation hard devices Status reports LHC under first beam conditions

### 150 Posters...

# Outline

| Power                              | 5   |

|------------------------------------|-----|

| Pixels                             | 9   |

| FPGAs                              | 15  |

| Silicon and Avalanche Photo-diodes | 18  |

| HEP in Germany                     | 21  |

| The Free Electron Laser            | 27  |

| Multi-projects, ASICS, 3D          | 42  |

| Fast optical serial links          | 49  |

| Data Acquisition, Xtca             | 68  |

| 3D, new interconnect technologies  | 77  |

| Parallel computing                 | 87  |

| Radiation Hardness                 | 90  |

| ATLAS Silicon detectors upgrade    | 92  |

| Triggers                           | 100 |

| LHC Status and Plans               | 106 |

| A 20 GS/s                          | 112 |

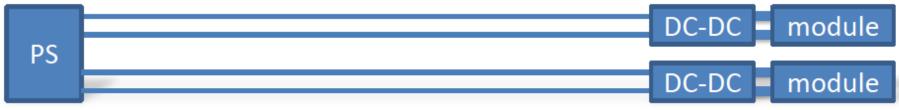

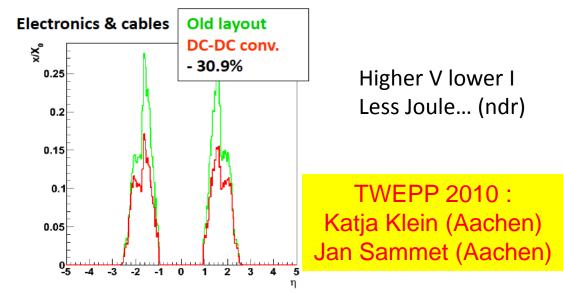

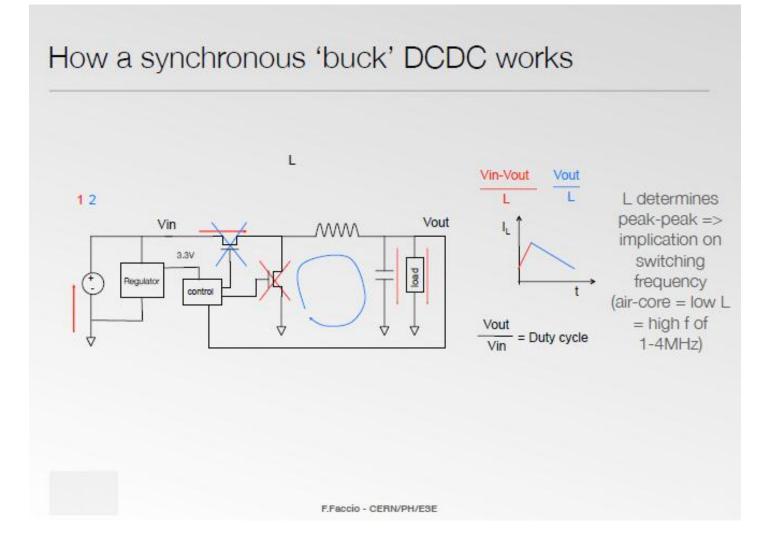

# Power DC-DC Converters vs Serial

#### DC-DC Powering CMS Tracker (Aachen)

Jean-Francois Genat, LPNHE Paris, October 24th 2010

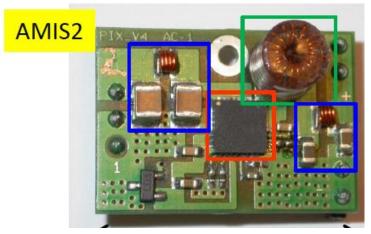

Radhard (MGy) AMIS2 Chip by CERN DC-DC System with aircore coil (4T CMS field)

$$V_{in} = 3-12 V$$

$I_{out} < 3A$

$V_{out} = 1.2, 2.2, 3.3 V$

$f_s = 600 \text{ kHz} - 4\text{MHz}$

6

## DC to DC ASIC

ASIC: Latchup and Radiation Hardness problems (ndr)

#### Federico Faccio (CERN)

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

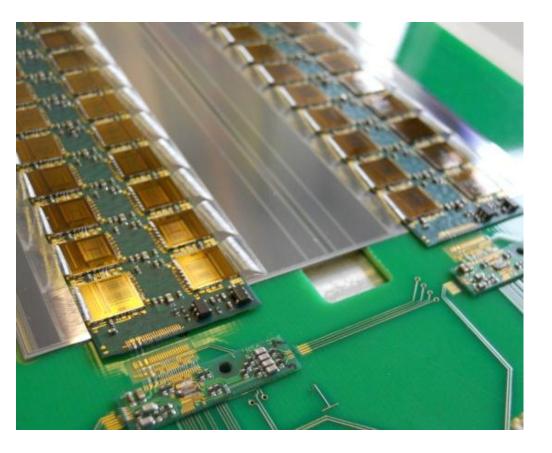

## Silicon strips for the ATLAS upgrade

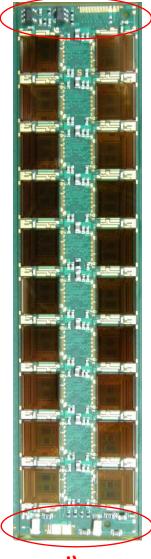

### Stave Hybrid – Layout and Electrical Detail

- Hybrid is designed to accommodate 20 x ABCN-25 readout ASICs (2 columns of 10)

- Layout topology matches ATLAS07 large area sensor and serially powered Bus cable

- ASICs placed to match sensor pitch and bond pad profile

- Hybrid Power and Digital I/O bond fields at opposite ends

- Circuit exploits features of ABCN-25

- Bi-directional data paths

- Embedded distributed shunt regulators (for serial powering)

- Requires external control circuit

Mshunt control and Digital I/O

Hybrid Power and sensor HV filtering (spec'd to 500V) 8

Jean-Francois Genat, LPNHE Paris, October 24th 2010

Ashley Greenall (U Liverpool)

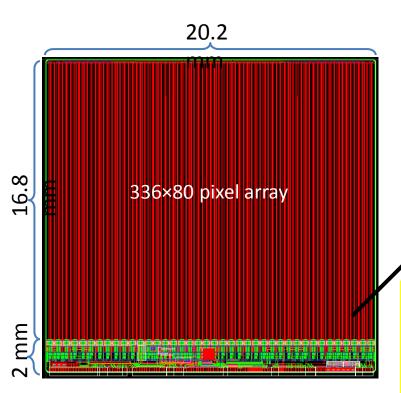

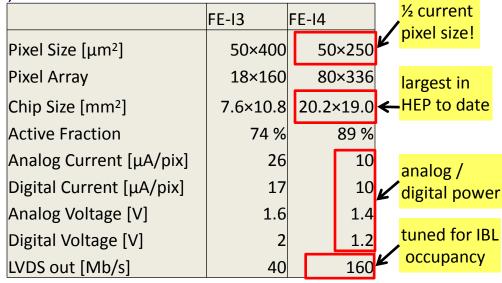

## **Pixels**

## ATLAS Pixels

Frontend FE-I4 for ATLAS pixel detector upgrades IBL Project (2014) and sLHC Common design effort: Bonn, CPPM, Genua, LBNL, NIKHEF

- Rad.-hardness >200 MRad TID (FE-I3: >50 Mrad)

- ToT coded in 4 bits.

- detector leakage current > 100 nA

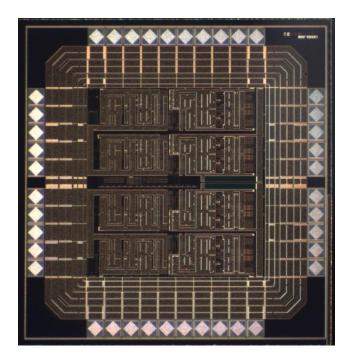

• Full scale engineering prototype: FE-I4A

TWEPP 2010 : Vladimir Zivkovic (NIKHEF) Laura Gonella (Bonn) Jens Dopke (Wuppertal)

Karlheinz Meier (U Heidelberg)

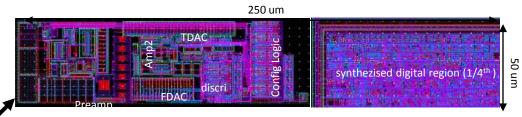

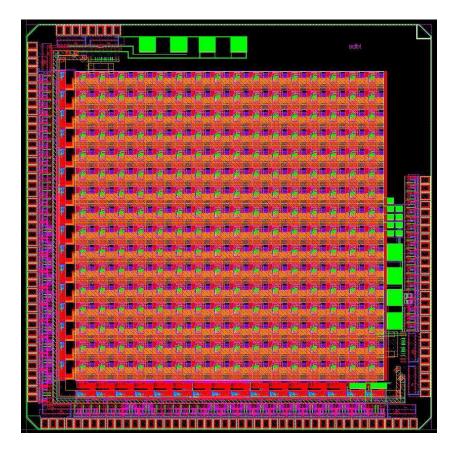

## ATLAS sLHC Pixel Upgrade : 3D Technology for Smaller Pixels

- Collaboration of Bonn (Germany), CPPM (France) and LBNL (USA).

- <u>Goal</u>: 50×125 µm<sup>2</sup> pixel size with split analog and digital functionalities

- <u>Technology</u>:

- Chartered 130nm

- Tezzaron 3D

- Prototype submitted in std.

Chartered 130nm technology as a test bench: → Good performance

- <u>3D analog + digital stack submitted</u>, processing has started

#### Karlheinz Meier (U Heidelberg)

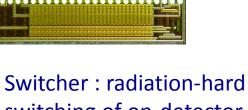

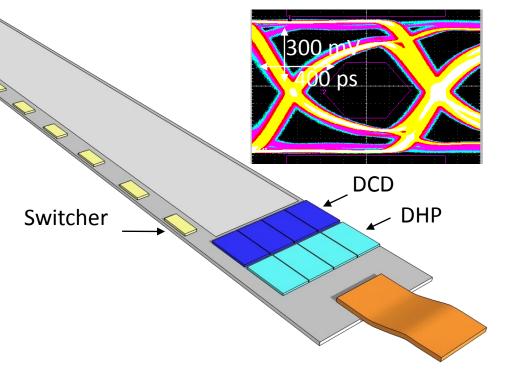

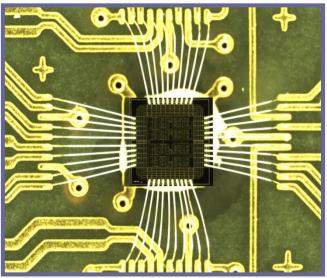

# Belle DEPFET Vertex DetectorKarlheinz Meier (U Heidelberg)Complete Electronics Chain (Barcelona, Bonn, Heidelberg)

Data handling processor DHP 0.1 (IBM 90nm) C4 bump bonds, full data processing, Gbit link, Analog blocks (U Barcelona)

switching of on-detector 20 V signals

DEPFET Current Digitiser (DCD) 256 channels, 10-bit, 10 MHz ADCs, 65 400 MHz Links

TWEPP 2010 : Jochen Knopf (Heidelberg)

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

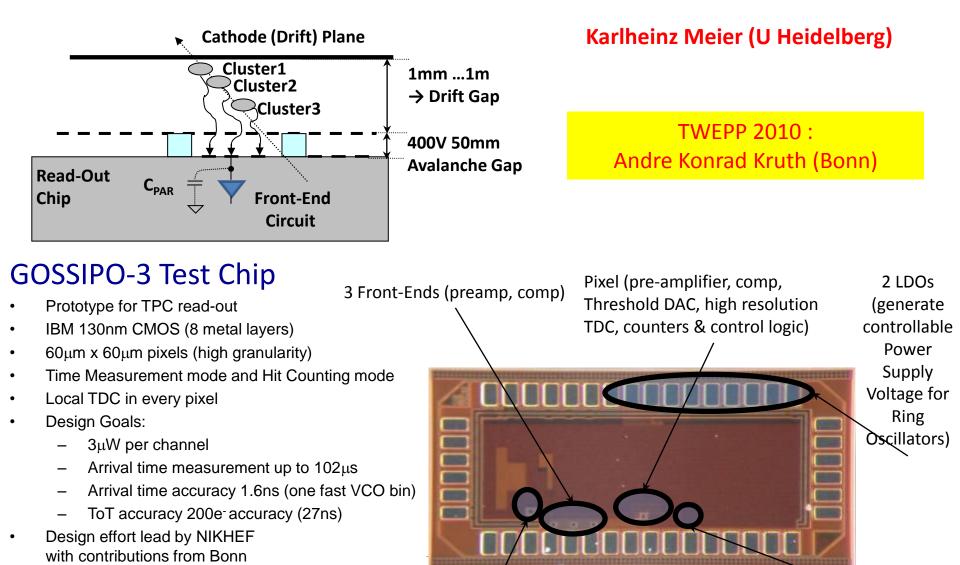

### Read-Out of Micro-Pattern Gas Detectors Gas-avalanche detector with a CMOS readout pixel array (ILC Study) Bonn, NIKHEF

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

Ingrid preamp

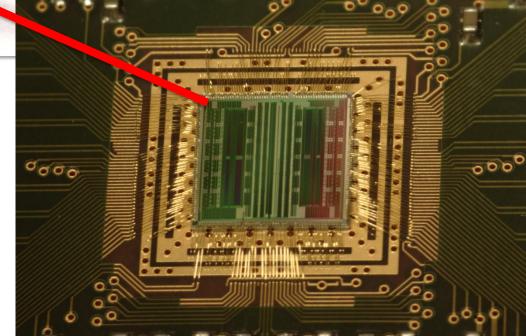

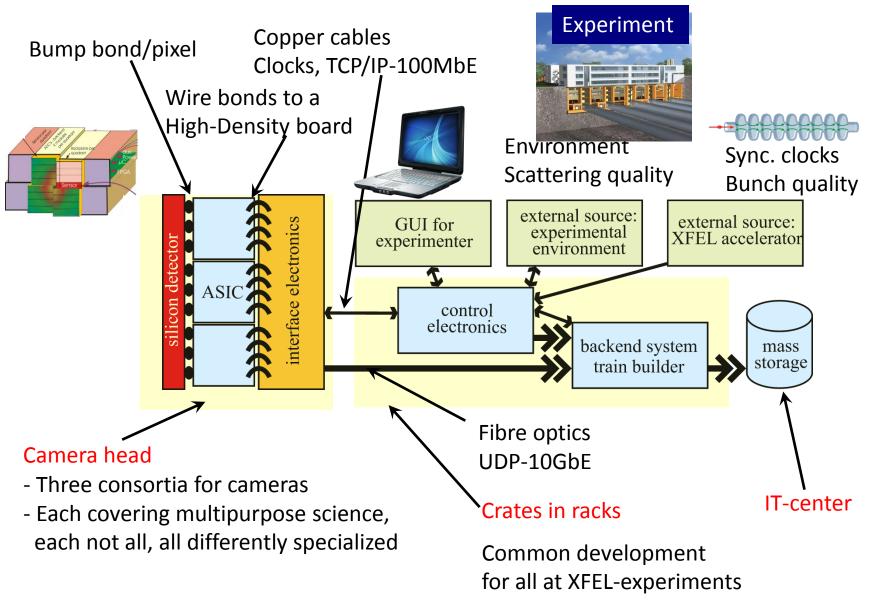

### AGIPD (Adaptive Gain Integrating Pixel Detector) for XFEL (DESY) DESY Hamburg und Bonn University

### Challenges

> high dynamic range (1 - 1.4 x 10<sup>4</sup>)

> single photon sensitivity,

> long storage chain (≥ 200)

> long hold time (99 ms)

> high radiation dose (up to 100 MGy)

Prototype test chip with a 16 x 16 pixel matrix 130nm (IBM cmrf8sf DM) CMOS technology 10 x 10 storage cells / pixel.

#### TWEPP 2010 : Peter Goettlicher (DESY)

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### Karlheinz Meier (U Heidelberg)

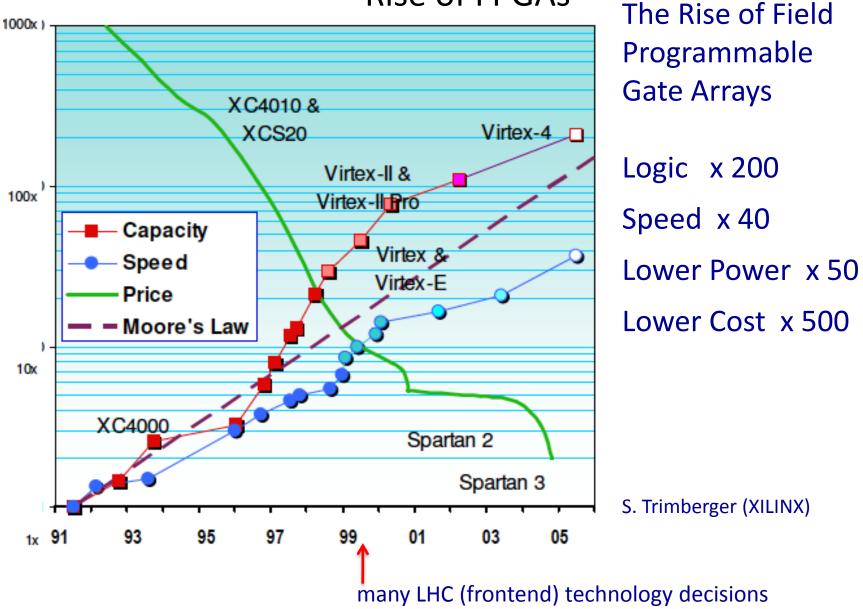

## **FPGAs**

**Karlheinz Meier (U Heidelberg)**

**Rise of FPGAs**

#### ATLAS – Level-1 Calorimeter Trigger Upgrade (Heidelberg)

#### SPARTAN- THE 6<sup>th</sup> GENERATION

low-power 45nm 9-metal copper layer dual-oxide process technology

150,000 logic cells

integrated PCI Express<sup>®</sup> blocks 250 MHz DSP slices

3.125 Gbps low-power transceivers

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### **Karlheinz Meier (U Heidelberg)**

# Silicon Photo-Multipliers Avalanche Photo-diodes

## Silicon Photomultiplier Readout Systems U Heidelberg

KLauS: Charge Readout Chip [Kanäle für Ladungsauslese von SiPMs]

CALICE

AMS 350nm CMOS technology; 4 channels; SPI interface controlled by FPGA; Bias DAC tunable; high Signal/Noise Ratio [>10, 40 fC signal charge]; fast trigger available [pixel signal jitter < 1ns]; large dynamic range up to 150pC

Upgrade version to be part of SPIROC III S. Callier et. al, IEEE NSS/MIC, 2009; 0.1109/NSSMIC.2009.5401891

PET and ToF

#### STIC: SiPM Timing Chip [Fast Discrimination for ToF]

AMS 350nm CMOS , 4 channels; Leading edge & Constant fraction Trigger; Bias DAC tunable ~ 1 V; power < 10mW/ch Pixel jitter ~300 ps, time of flight capability

W. Shen et. al, IEEE NSS/MIC, 2009; 10.1109/NSSMIC.2009.5401693

#### Karlheinz Meier (U Heidelberg)

### Readout of APD Array for PET-MR (U Heidelberg)

#### **Karlheinz Meier (U Heidelberg)**

#### 40 Channel Readout Chip

- ➢ fast low-noise differential amplifiers

- ➢ O(100µV noise)

- time stamping with 50ps binwidth

- ➢ integrator

- > 9Bit ADC

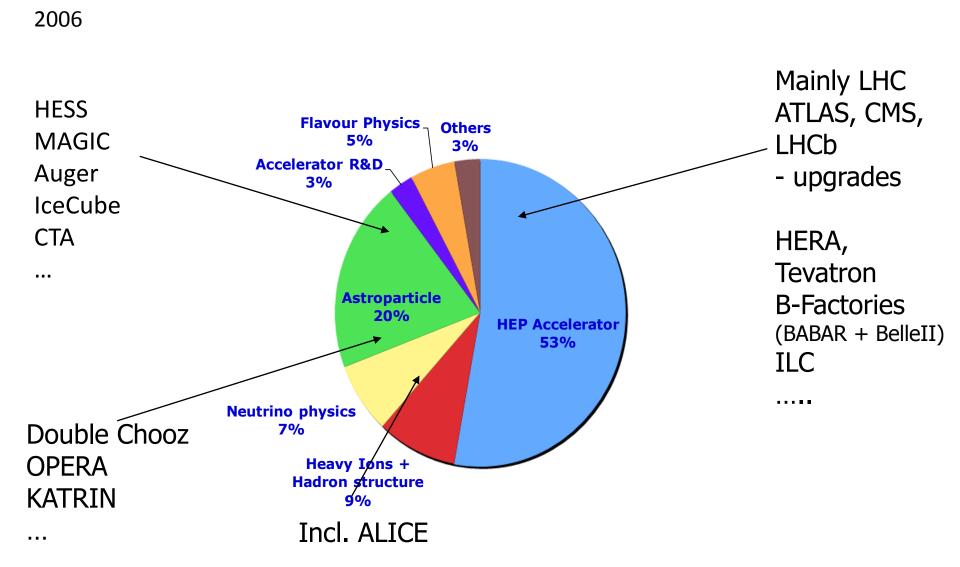

## **HEP in Germany**

## Particle Physics in Germany

+ R&D on Accelerator, detector, (Grid) computing

Bernhard Spaan (TU Dortmund)

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

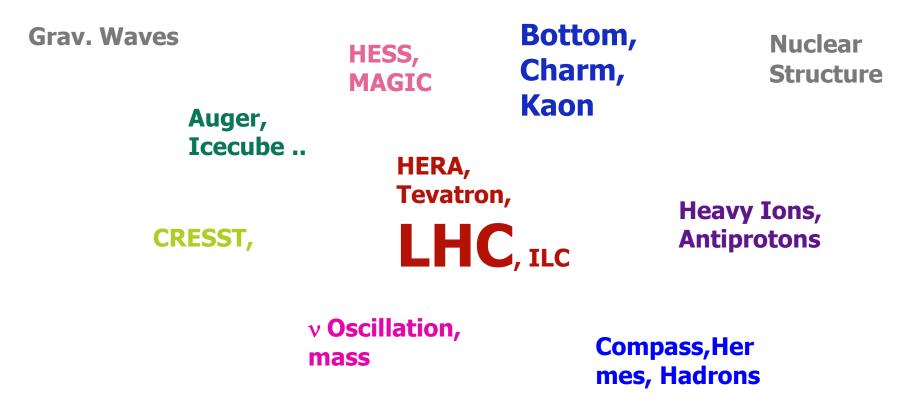

# Fields of Research (HEP)

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### **Bernhard Spaan (TU Dortmund)**

23

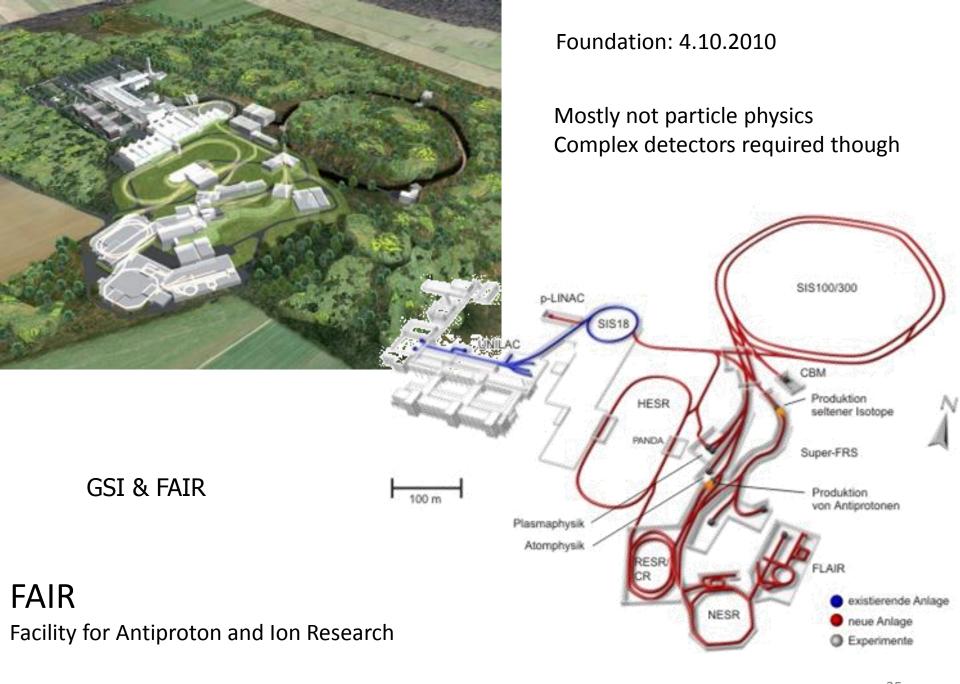

## DESY

Changing role of DESY

Now: no operating accelerator for particle physics accelerators at DESY  $\rightarrow$  photon science

HERA data still being analyzed

Still vital for particle physics in Germany

- central facilities

- (e.g. Tier-2 Center for ATLAS, CMS, LHCb)

- National Analysis Facility

- Heart of the Helmholtz-Alliance

#### Bernhard Spaan (TU Dortmund)

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

### Bernhard Spaan (TU Dortmund)

## Conclusions

Strong research in particle physics

Strong focus on LHC programme (incl. Upgrade)

DESY changed profile – still vital for particle physics Free Electron Laser development (ndr)

Somewhat complicated structure/funding regime

Participation in all areas -

- Detector R&D and construction

- Electronics

- Data Analysis

- Computing

- Accelerator Physics

Future strategy in preparation

#### Bernhard Spaan (TU Dortmund)

Jean-Francois Genat, LPNHE Paris, October 24th 2010

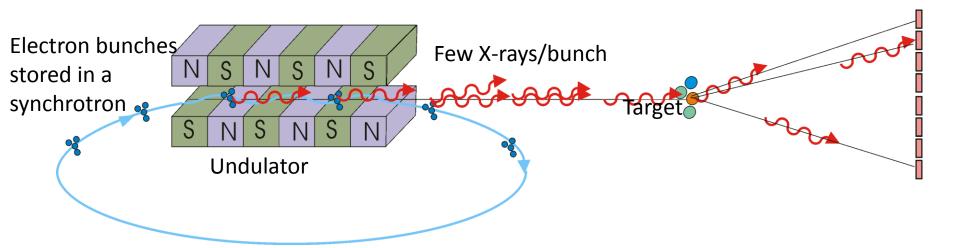

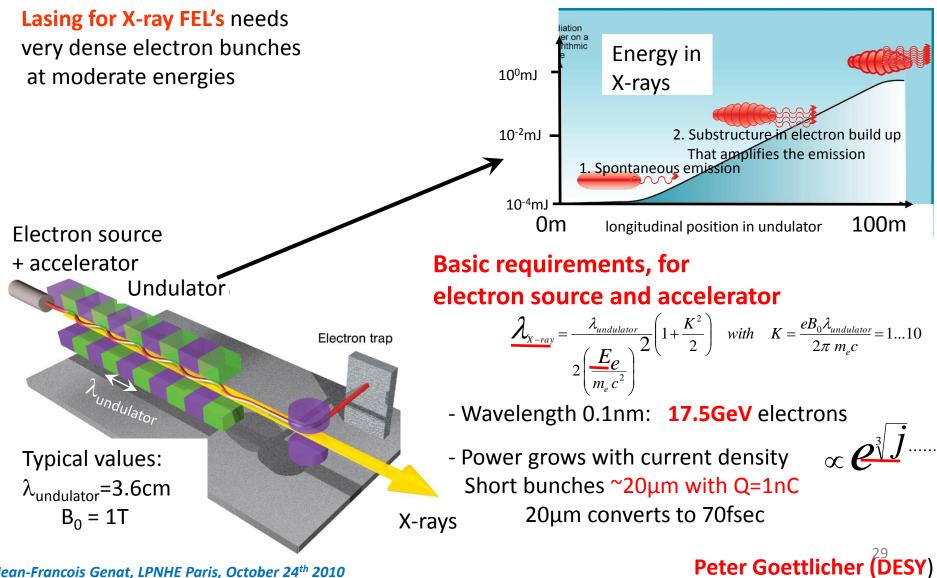

## The Free Electron Laser (FEL)

## Science with X-ray from nowadays synchrotrons 3<sup>rd</sup> Generation

- Nice systems, but more wishes for the future

- Intensity

- Coherence for holography

- Many photons/bunch in <100fs:</p>

- $\Rightarrow$  Get the picture before X-rays destroy the target

#### **Imaging detectors:**

e.g. Pilatus: 2-dimensional pixel Counting: 1MHz/pixel Rate: 10-100 pictures/sec

### The Free Electron Laser The SASE principle

Self amplified spontaneous saturation emission

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

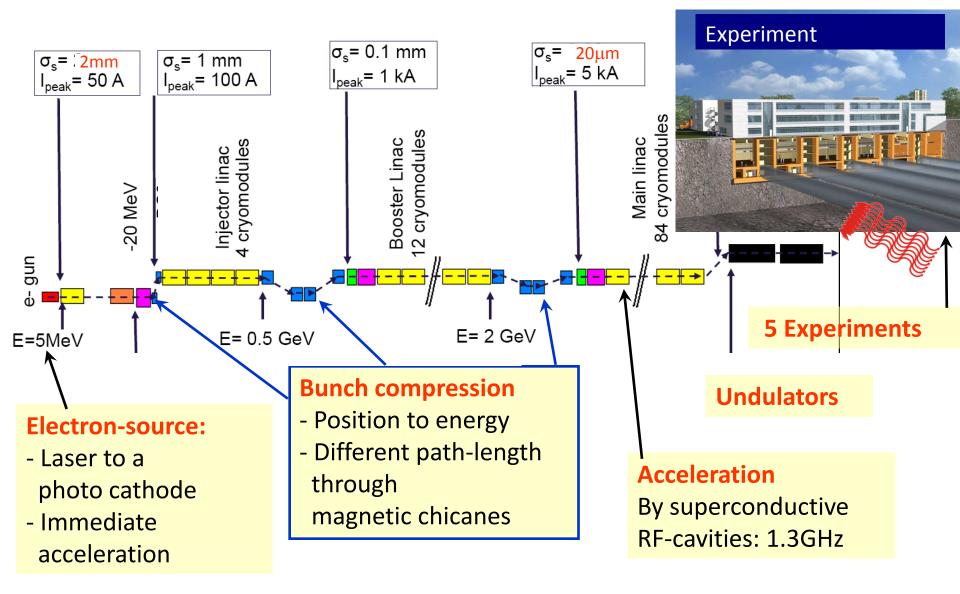

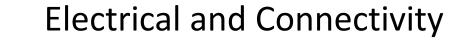

## **XFEL: Functional blocks**

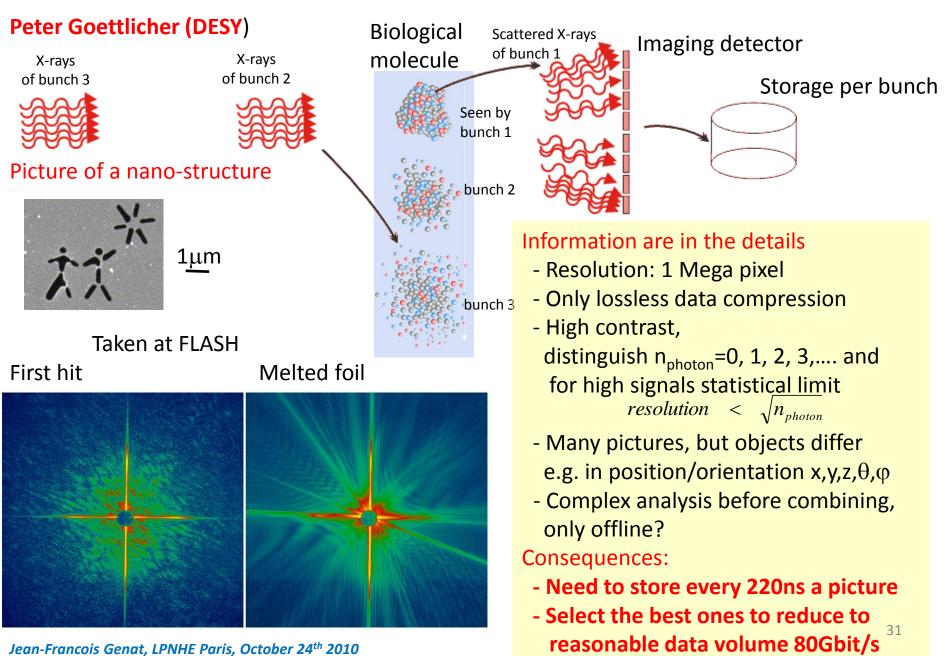

## Detectors for the dream: 2-dimensional cameras

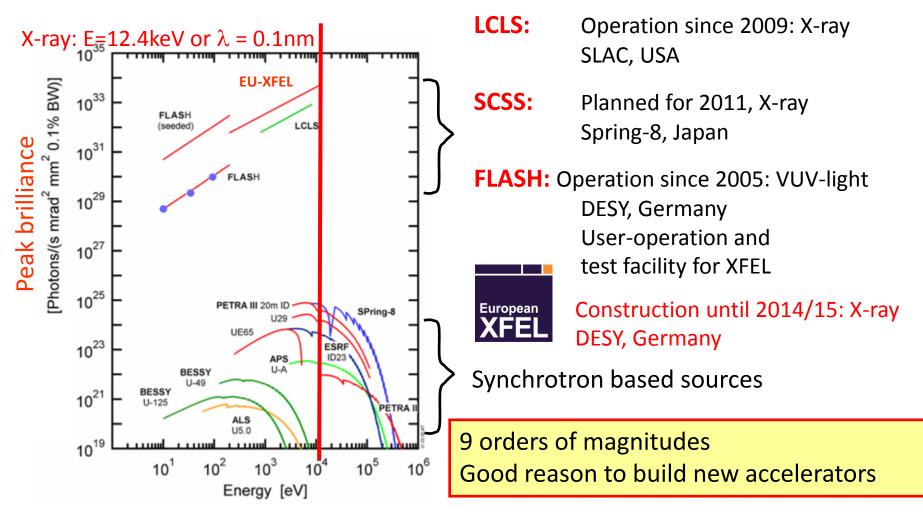

# Comparison: From synchrotrons to FEL's

Intense light gets delivered by lasers, now lasing for X-ray

#### **FEL based sources**

#### Peter Goettlicher (DESY)

#### Jean-Francois Genat, LPNHE Paris, October 24th 2010

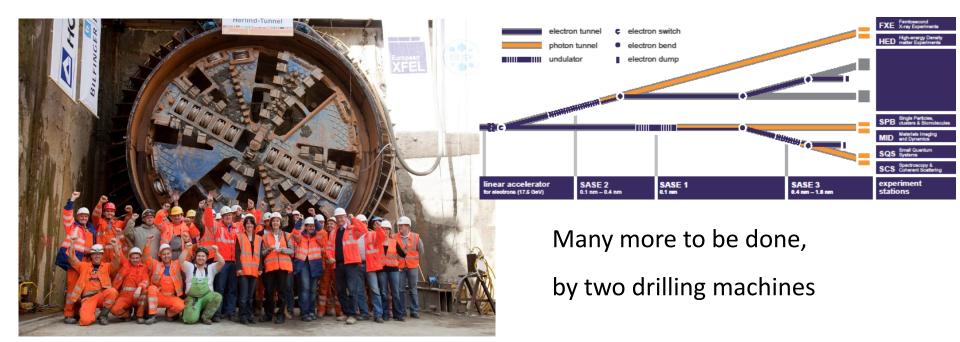

## The European XFEL:

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### Peter Goettlicher (DESY)

### General detector concepts:

Peter Goettlicher (DESY)

<sup>h</sup> 2010

### 2-dimension cameras

#### Adaptive Gain Integrated Pixel Detector

AGIPD Institutes: Bonn(University), DESY, Hamburg(University), PSI(Villingen) Reference: B. Henrich, et al., Nucl. Instr. and Meth. A (2010), doi:10.1016/j.nima.2010.06.107

#### **DEPMOS Sensor with Signal Compression**

DSSC Institutes: MPI-HLL Munich, DESY, Heidelberg(Univ.), Poly. Milano, Bergamo(Univ.), Siegen(Univ) Reference: M. Porro, et al., Nucl. Instr. and Meth. A (2010), doi:10.1016/j.nima.2010.02.254

#### Large Pixel Detector

Institutes: STFC/RAL, Glasgow(University)

LPD Reference: S.R.Burge et al., Large Pixel Detector for the European X-ray Free Electron Laser, 11th European Symposium on Semiconductor Detectors, June 2009 conference proceedings.

#### **Common items**: Sensor-studies, **ASIC in 130nm-technology,** DAQ-systems

#### Different physics by different technical approaches

|                            | AGIPD                          | DSSC                              | LPD                             |

|----------------------------|--------------------------------|-----------------------------------|---------------------------------|

| Pixel                      | 200 x 200μm²                   | 236µm hexagons with a DEPFET      | 500 x 500μm²                    |

| Approach for dynamic range | Automatic gain switching       | Compression by<br>DEPFET in pixel | 3 parallel gains                |

| Storage per<br>bunch       | Analogue with analog ASIC-out. | Digital,<br>1ADC/pixel            | Analogue with digital ASIC-out. |

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### Peter Goettlicher (DESY)

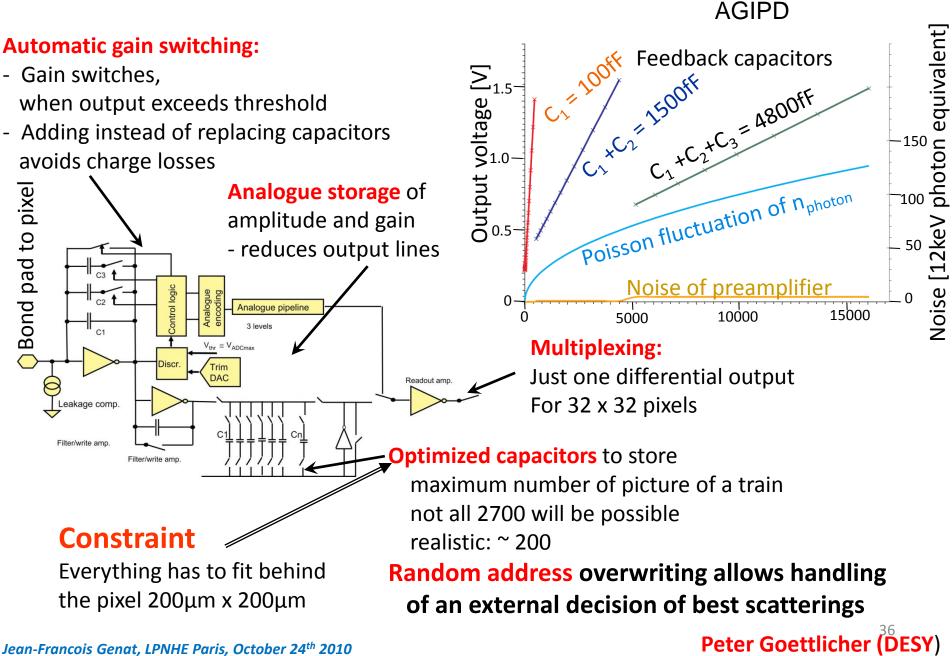

## **Camera Analog ASIC**

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

# Signal rates

#### Peter Goettlicher (DESY)

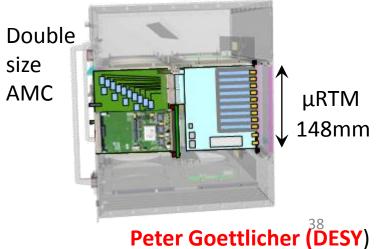

# xTCA as platform

High performance digital standard: Telecommunications

- ATCA: Advance Telecommunication Computing Architecture: 2002

### Features:

- Backplane: many multi gigabit serial links

- Configurable network

- Redundancies: Power, CPU, MCH

Reliability >99.999%

- Carriers for 1-8 AMC Advance Mezzanine Cards

- Hot swap

μTCA Scalable to - Small systems

- Features like ATCA

- modules = AMC's

A standard for physics - Science ( TFEL + Industry )

### Features:

- Based on  $\mu$ TCA

- More space

- Synch. clocks on backplane

- Rear access by μRTM's

μRear Transition Modules

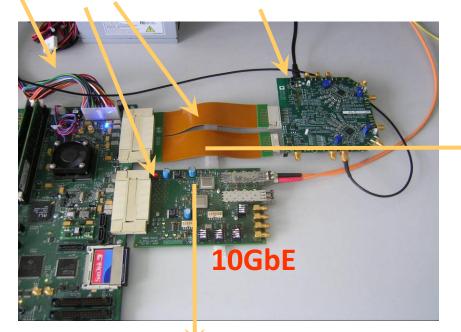

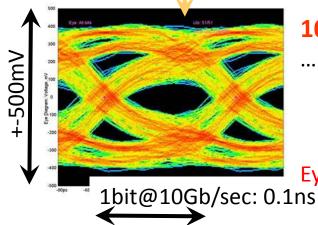

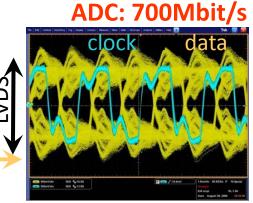

## Evaluation of high speed data transfers

XILINX evaluation board + custom VHDL-UDP-core +custom designs+ ADC-evaluation board

### **10 Gbit-Ethernet**

... Measurement is limited by 16GHz-scope Performance is better Eye diagram is well open

Performance limited by no-impedance on XILINX-evaluation board Eye diagram is well open

### Links are OK.

- Need no ideal setup

- Freedom to optimize system setup mechanics, modularity,...

## **XFEL** status

- European XFEL will deliver the highest peak brilliance and bunch rate.

- Need of excellent accelerator performance: Size and energy of bunch.

- Dedicated regulations in modern technologies needed.

Developments and tests at FLASH are on going with good results.

- That leads to the use of modern standards in science: ATCA, μTCA.

Adapting them to the needs (PICMG®) and first modules are available.

- Demanding dedicated detectors (Pixel cameras) are being developed.

Ongoing developments for full chain with high signal and data throughput:

- Sensors, ASIC's, detector heads and DAQ systems

- e.g. 4.5MHz picture rate, 80 Gbit/s out of small detector heads

- All the effort opens new fields of science:

Capturing a scattering picture with one flash of X-rays.

- Thanks to all the work packages and consortia for providing material

- More information on

www.xfel.eu

http://hasylab.desy.de/instrumentation/detectors/index\_eng.html

## **XFEL plans**

- 2012 Buildings getting ready for installation

- 2013 First beam in injector

- 2014 First beam in linear accelerator

- 2015 First SASE, first experiment

- 2016 'Full' User operation

# Multi-projects, ASICS, 3D

### **CERN Microelectronics Users Group**

- IBM 130nm design kit version 1.7

- Scripts for mixed design available

- Develop a scripted design for digital core circuits with separate substrate ground for low noise applications.

- Develop an IP library in IBM 130nm CMOS

#### Forthcoming MPW runs:

CMOS6 (250nm) Tape Out beginning of next year. Support for 3 and/or 6 metal stacks. CMOS8RF (130nm) MOSIS Nov. 8, 2010 CMOS9LP/RF (90nm) MOSIS Dec. 8, 2010

#### Forthcoming AMS Workshops

Week of Oct. 18-22 End of 2010

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

#### **Kostas Kloukinas (CERN)**

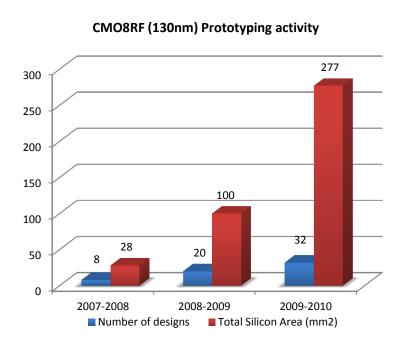

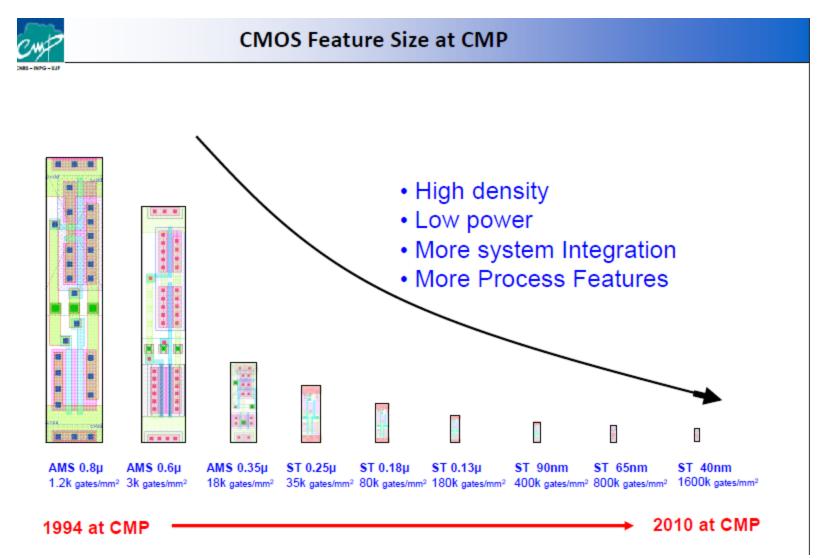

## CMOS feature size evolution 1994-2010

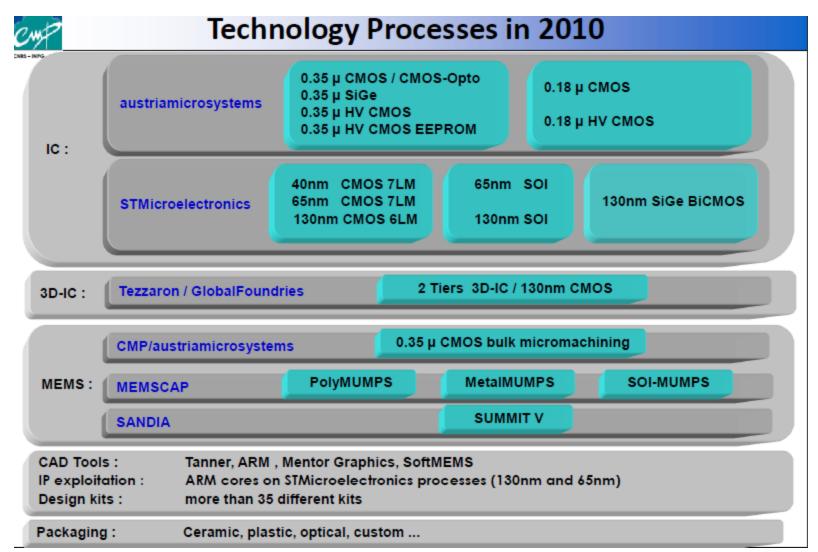

#### Kholdoun Torki (CMP Grenoble)

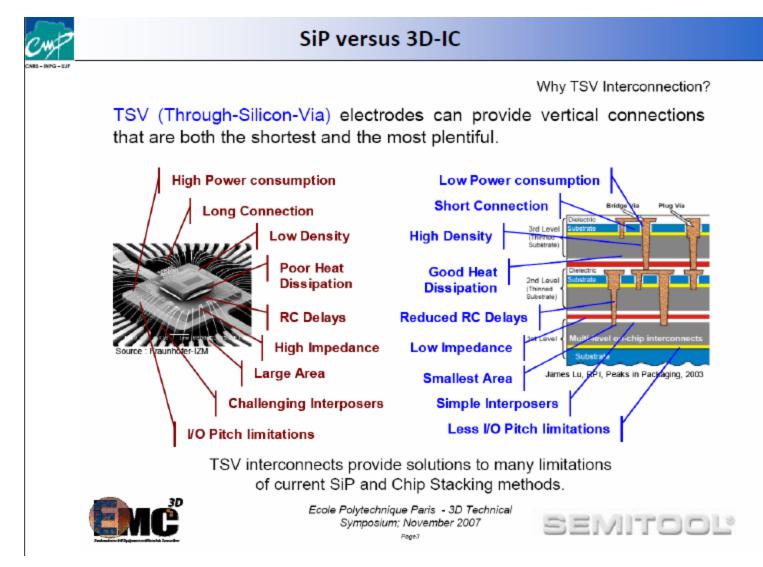

## Conventional interconnections versus 3D

#### Kholdoun Torki (CMP Grenoble)

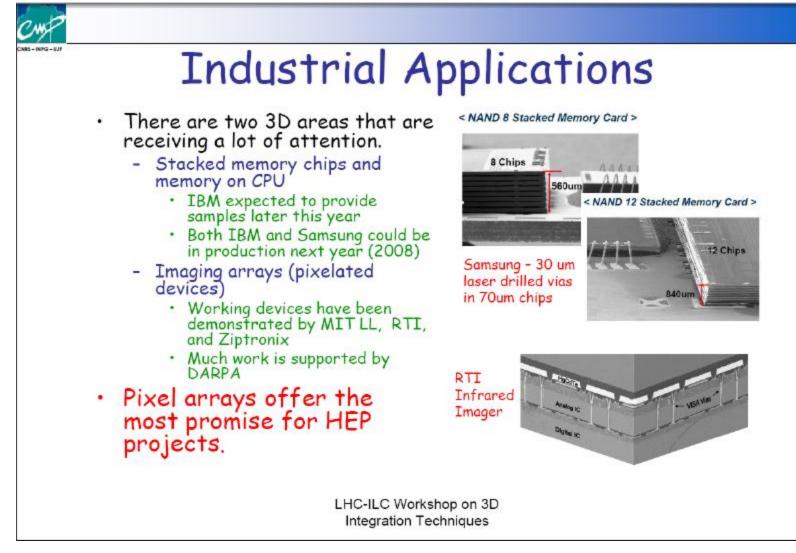

## **3-D MPW Industrial Applications**

#### Kholdoun Torki (CMP Grenoble)

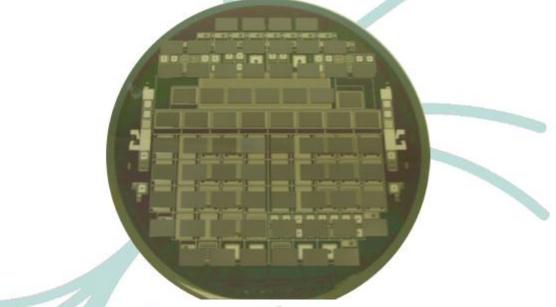

## 3-D Multi-Project Wafers runs for HEP

#### Kholdoun Torki (CMP Grenoble)

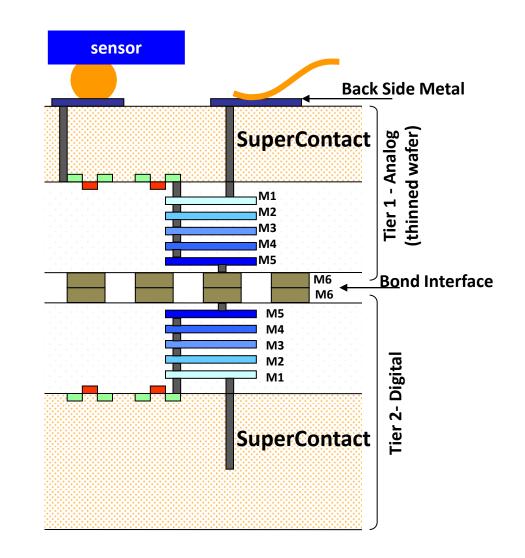

### **3-DMPW Access**

CMP/CMC/MOSIS partner to introduce a 3D-IC process

Grenoble, France, 22 June 2010, CMP/CMC/MOSIS are partnering to offer a 3D-IC MPW service based on Tezzaron's SuperContact technology and GLOBALFOUNDRIES 130nm CMOS.

The first MPW run is targeting January 2011:

- 2-tier face-to-face bonded wafers

- 130nm CMOS process for both tiers

- Top tier exposing TSV and backside metal pads for wire bonding.

A design-kit supporting 3D-IC design with standard-cells and IO libraries is available.

Further MPW runs will be scheduled supporting process flavors (multiple tiers beyond

2, different CMOS flavors for different tiers, ...) driven by user requirements.

Potential users are encouraged to contact CMP for details : cmp@imag.fr

#### Kholdoun Torki (CMP Grenoble)

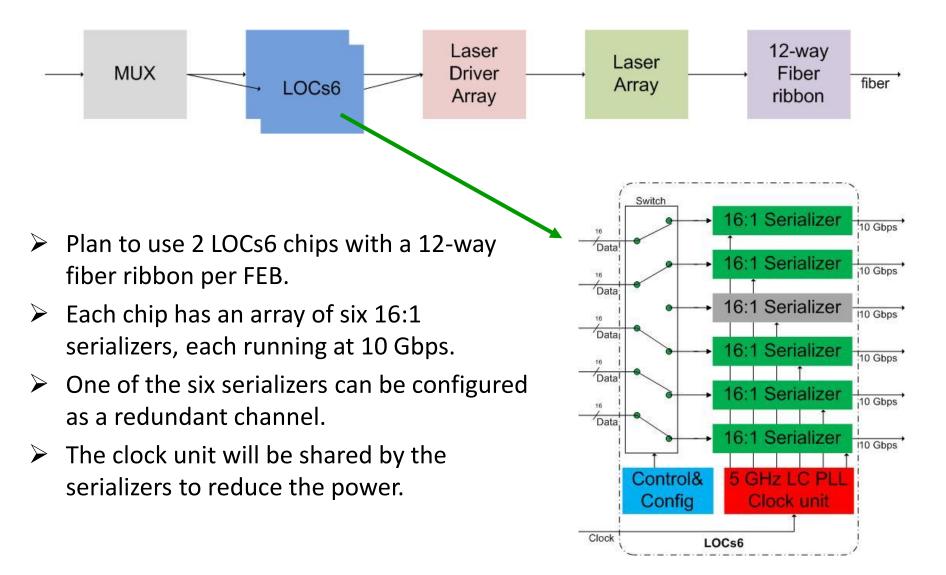

# Fast optical serial links

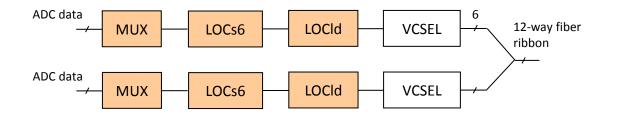

## LOC6 project

Proposed for the upgrade ATLAS/LAr FEB optical link: 100 Gbps/FEB bandwidth = 62× LHC

ASIC technology as 0.25 μm silicon-on-sapphire CMOS technology commercially available, MWP runs ~ 6 /year.

- Serdes-embedded FPGAs as receiving side benefits from the Versatile Link common project: optical interface and system design.

- Most challenging part: serializer, a 6-lane array serializer with redundancy switches at 10 Gbps.

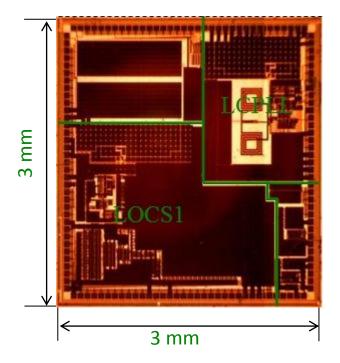

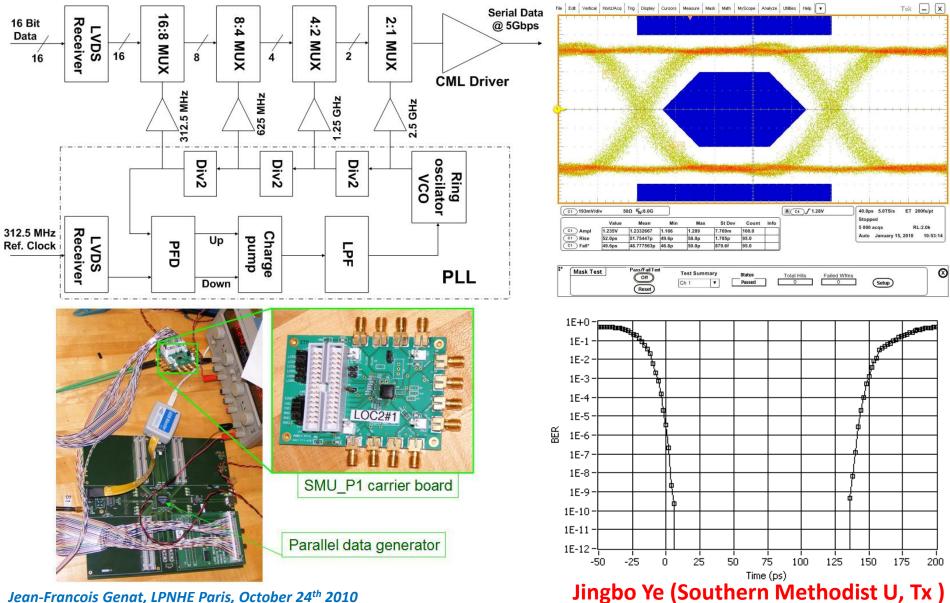

# LOC1 Serializer ASIC

- Serializer:

- Prototype chip submitted August 2009.

- 3 × 3 mm2 comprising

- LOCs1, a 5 Gbps 16:1 serializer.

- LCPLL, a 5 GHz LC VCO based phase locked loop.

- A CML driver

- A divide-by-16 circuit.

- Varactor, Voltage controlled capacitor.

- SRAM block

# Test results of LOCs1

# Next version ASIC — LOCs6

### Jingbo Ye (Southern Methodist $\overset{53}{U}$ , Tx )

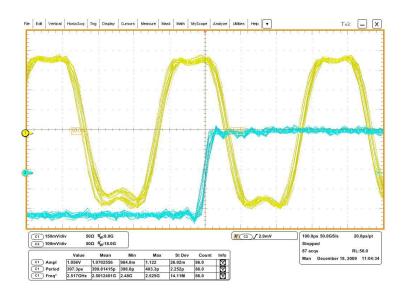

# 5 GHz LC PLL

### Fabricated in the same die as LOCs1 is a 5 GHz LC PLL

### •Tuning range: 4.7 to 5 GHz.

- Expected: 3.79 to 5.01 GHz.

- Cause traced to the divider in PLL and will fix in the next design.

#### Power consumption: 121 mW

- Compare: Ring oscillator based PLL, 173 mW at 2.5 GHz

- •Random jitter: 1 2.5 ps (RMS)

- Deterministic jitter:< 17 ps (pk-pk)</li>

#### output clock locks to input clock

Jingbo Ye (Southern Methodist  $\stackrel{54}{U}$ , Tx )

# High speed CML circuit design

CML buffer for 5 GHz clock fan-out. More CML circuit components ongoing.

Parameters for the CML buffer:

- Frequ > 5 GHz

- Power: ~8 mW

- Two stage design

- Fan out two identical buffer without signal attenuation

#### PP < rt=1.231K PP rt=1.847K rt=1.231K rt=1.847K M1 4.7/Ø.25 mt=4 M2 4.7/Ø.25 mt=4 7.05/0.25 7.05/0.25 mt=4 RN RN 8.35/Ø.5

Schematic and Layout

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

### Jingbo Ye (Southern Methodist U, Tx )

# Plans and Summary

### Design of LOCs6

#### As of the LOC1 tests, more needed.

- More tests on LOCs1 are still needed

- First proton test on LOCs1 produced very good results.

- More tests may be needed to study SEE.

- Would like to investigate an array laser driver, LOCLD6

- Limited by manpower and resource. Need help in the development of the 100 Gbps/board system.

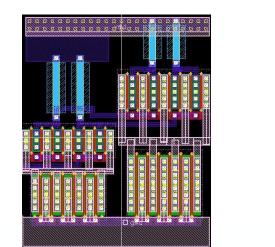

# Versatile Link Project

- Optical Physical layer linking front

to back-end

- Bidirectional, ~5Gbps

- Versatile

- Multimode (850nm) and Singlemode (1310nm) versions

- Point to Point and Point to Multipoint architectures

- Front-end pluggable module

- Joint Project Proposal submitted to ATLAS & CMS upgrade steering groups in 2007 and endorsed in 2008

- Kick-off mtg in April 2008

- Phase I: Proof of Concept (18mo)

- Phase II: Feasibility Study (18mo)

- Phase III: Pre-prodn. readiness (18mo)

**Off-Detector**

Custom Protocol

Commercial Off-The-Shelf (COTS)

DD-

**On-Detector** Custom Electronics & Packaging Radiation Hard

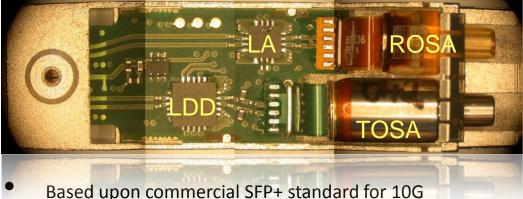

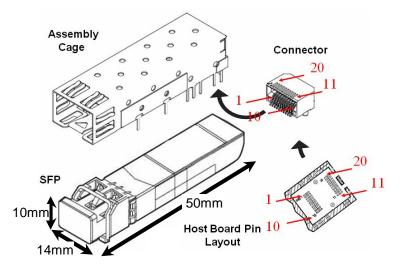

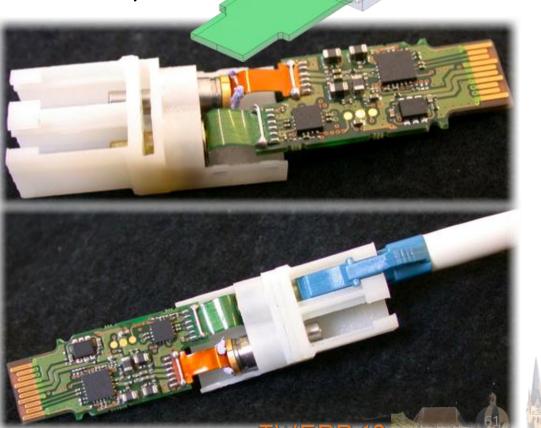

## VTRx packaging overview

Based upon commercial SFP+ standard for 10G transceivers

- ASICs

- Laser Driver (LDD) GBLD

- TIA GBTIA

- LA not foreseen (inc. in GBTIA)

- No microcontroller

- TOSA Rad Hard Laser

- ROSA Rad Hard PIN + GBTIA

- Keep Std. SFP+ Host board connector

- No cage, alternate fixing T.B.D.

- Remove/replace material from std. SFP+ housing

- Must test EMI tolerance and emission

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

**VTRx**

### Components

GBLD GBTIA Commercial LDD Commercial TIA/LA ROSAs 850/1310nm TOSAs 850/1310nm Device modelling

#### Pkg know-how

Commercial Eval Boards In-house Test boards Industrial partnership VTRx prototype board

Jan Troska (CERN)

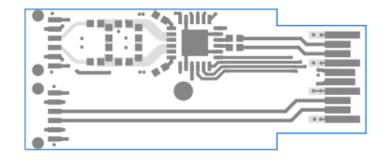

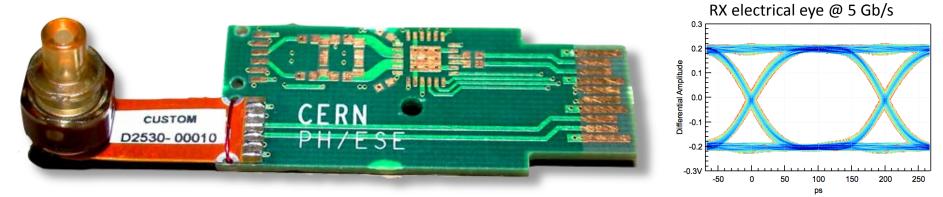

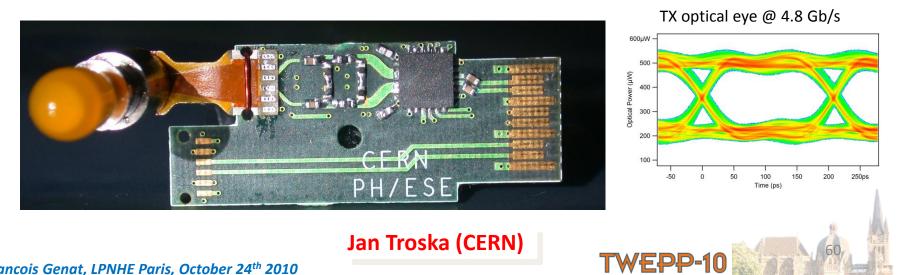

# VTRx PCB design

- Based upon experience gained with commercial ASIC evaluation boards and our own versions of such boards, have built our own SFP+ size-compatible test PCB housing:

- Commercial edge-emitting laser driver

- Commercial TOSA

- GBTIA-ROSA

- PCB circuit simulations including the laser model were carried out to confirm the correct functionality of the board

- Including optimization of the bias/matching network

## TOSA/ROSA integration on VTRx

**GBTIA-ROSA** on prototype VTRx PCB •

TOSA and commercial Laser Driver on VTRx PCB •

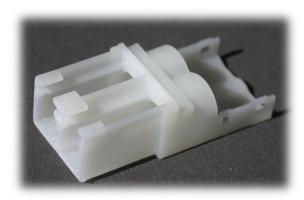

## VTRx low-mass latch design

- Working on mechanical design of VTRx connector latch to reduce overall mass of the transceiver

- Part mechanically associates connector and TOSA/ROSA

- Rapid prototype plastic samples successfully tested

### Jan Troska (CERN)

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

Versatile Link

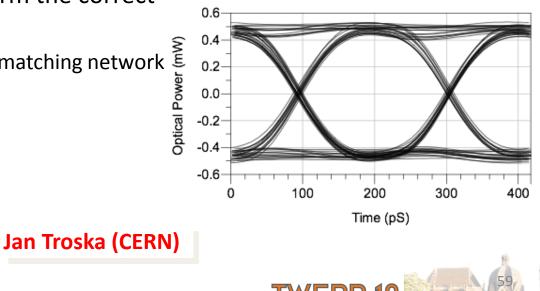

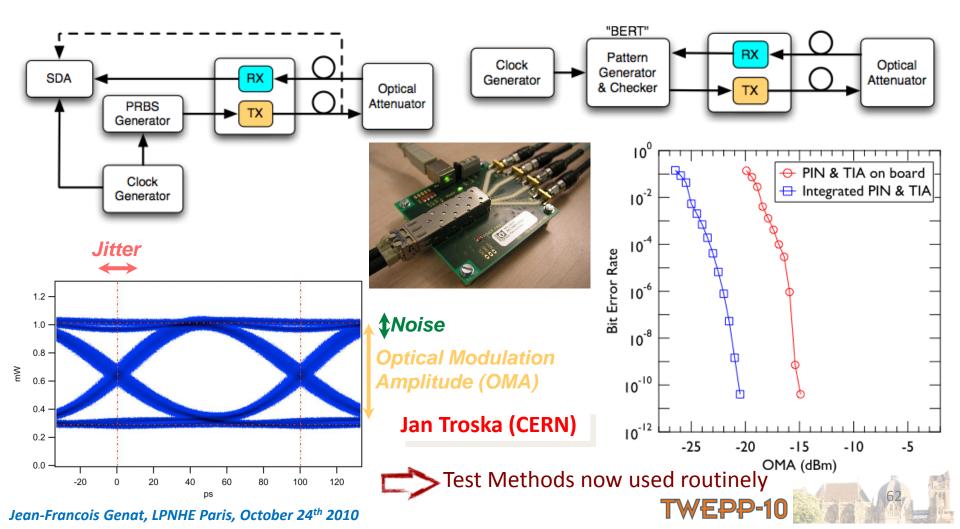

## **Functionality Testing Overview**

- Signal "Eye" Diagrams optical for TX, electrical for RX

- 2. Bit Error Test (BERT)

FR

Versatile Link

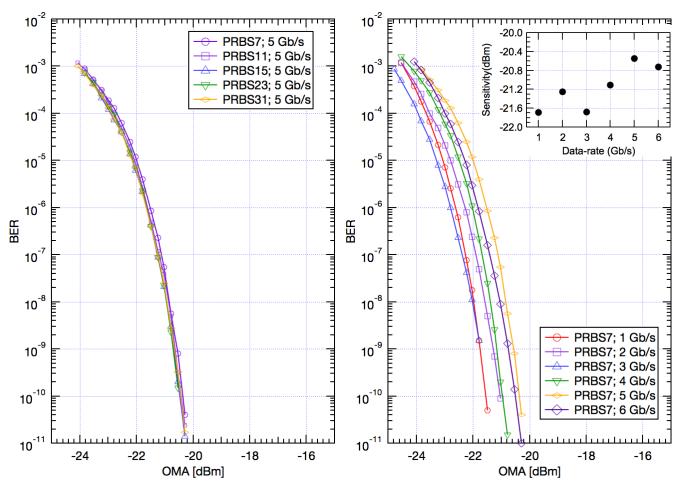

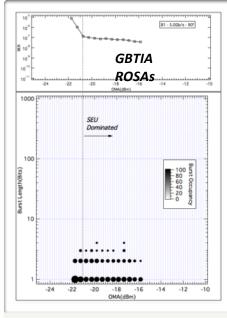

### **GBTIA ReceiverOSA performance**

Evaluate impact of data-rate and pattern length on GBTIA ROSA sensitivity

Favourable comparison to bare-die tests

Versatile Link

- ROSA pkg not detrimental to functionality

- No pattern length sensitivity

- Expected reduction in sensitivity with datarate

- Acceptable magnitude

### Jan Troska (CERN)

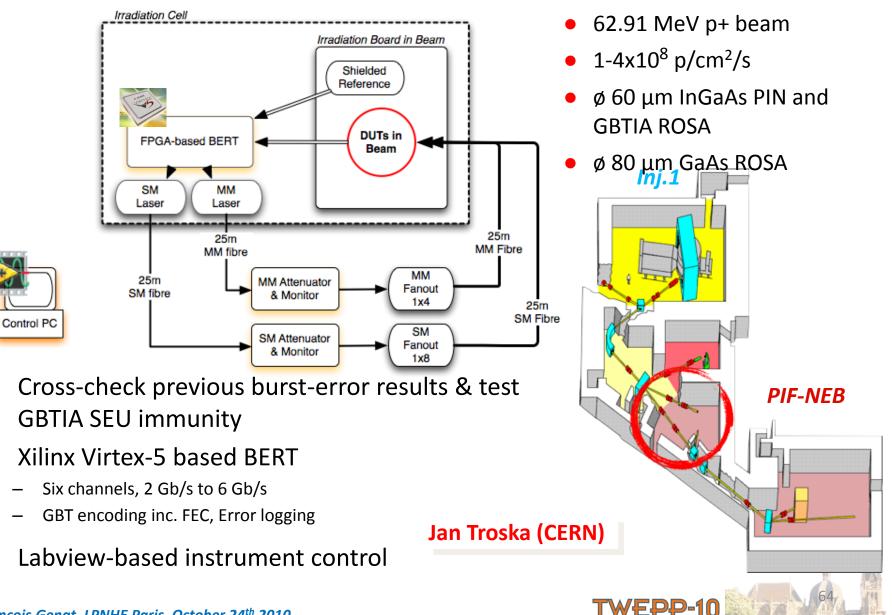

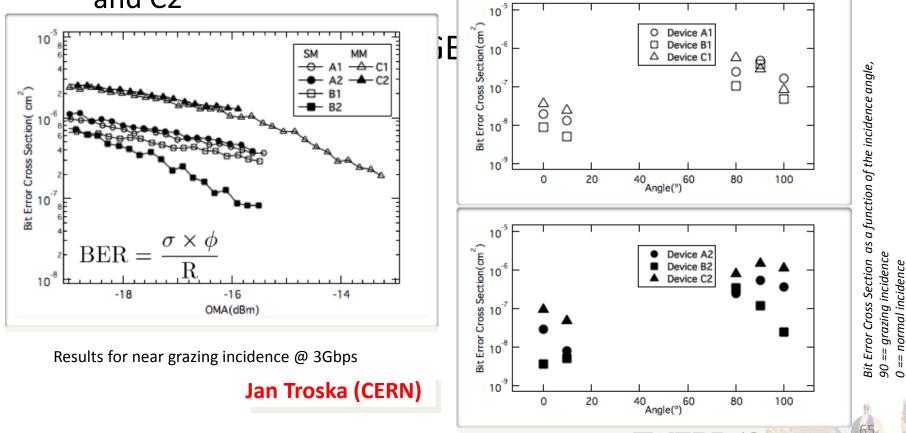

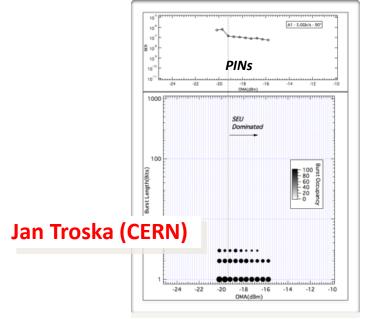

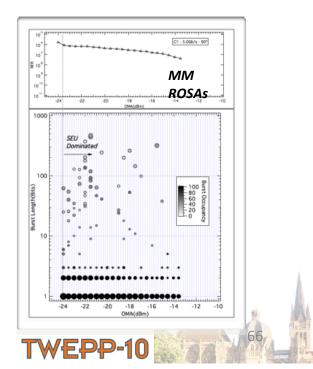

## **PSI Proton SEU Test**

SEU test result preview (1/2)

Versatile Link

- Similar overall trend but several orders of magnitude difference in response between devices

- SM PINs A1 and A2, GBTIA ROSA B1 and B2, MM ROSA C1 and C2

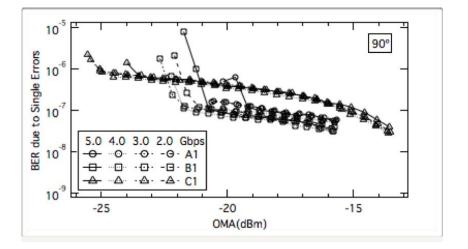

### SEU test result preview (2/2)

- BER due to single bit flips is similar for all devices

- BER is independent of data rate within the range of investigation

- Burst lengths limited in PINs and GBTIA ROSAs

- Longer bursts seen in ROSAs with unshielded amplifiers

## Summary & future work

- In terms of our Phase II deliverables

- Specifications for on-detector components

- Available and under discussion within Versatile link project, soon to be distributed more widely

- Packaging

- In-house development of both PCB and mechanical pkg progressing well

- Successful integration of GBTIA and PIN into ROSA

- Detailed measurements of multiple devices in near future

- Defining strategy for future variants (GBLD, TOSA types)

- Functional test methods applied to testing of transmitters and receivers

- Excellent performance of GBTIA ROSA

- Performance limitation of current VTRx design being studied in simulation

- Radiation Testing

- SEU test results compare well with previous results

- Burst errors not observed in GBTIA or high-speed commercial TIA

- Pion test carried out, lots of data to analyse

Jan Troska (CERN)

## xTCA

# Micro/Advanced Telecommunications Computing Architecture

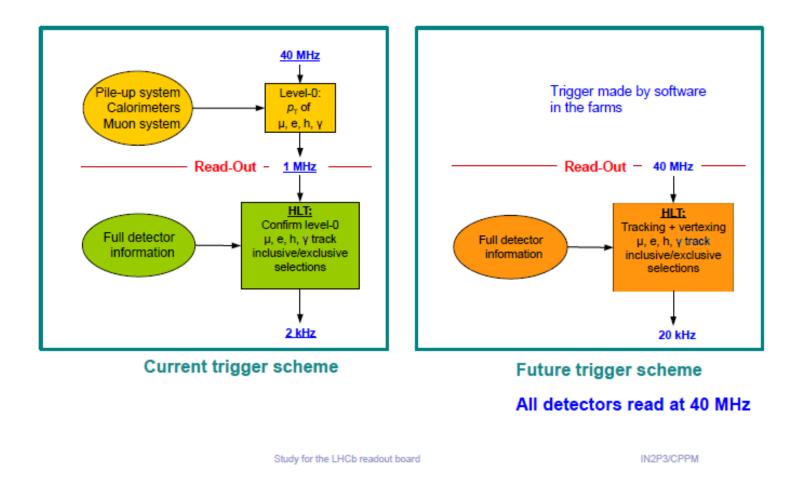

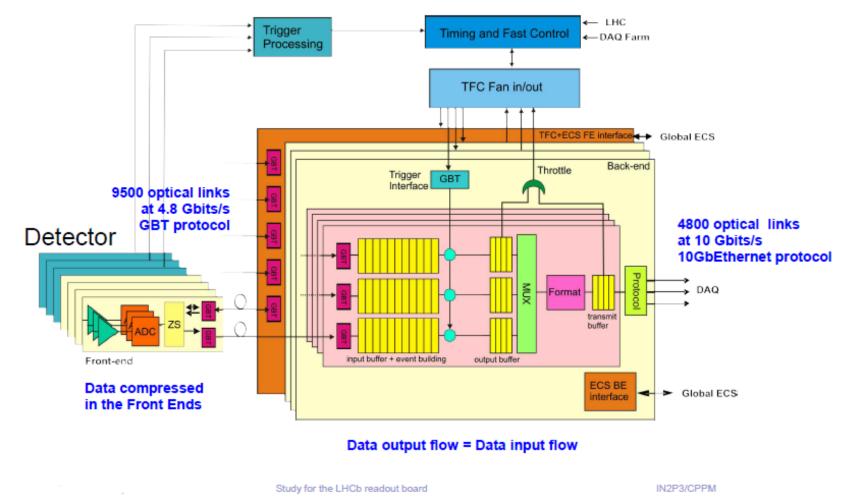

# LHCb Upgrade

### Outline

- LHCb Upgrade

- Building blocks for high speed read-out

- Performances

- Slow control

- Scalable read-out architectures

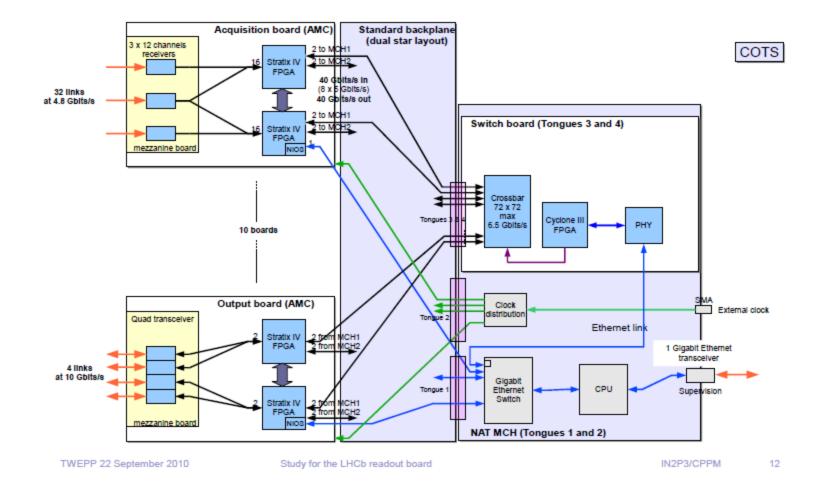

Study for the LHCb readout board

IN2P3/CPPM

#### J-P Cachemiche, CPP Marseille

# 40 MHz Front-end readout

### Trigger upgrade

#### J-P Cachemiche, CPP Marseille

# 40 MHz Front-end readout

### LHCb read-out requirements

J-P Cachemiche, CPP Marseille

# μ/ΑΤϹΑ

#### **Development based on xTCA**

#### ATCA carrier

TWEPP 22 September 2010

12-2-2

AMC card

Study for the LHCb readout board

ATCA

**µTCA**

IN2P3/CPPM

#### Powerful connectivity in xTCA standards

#### Study for the LHCb readout board

IN2P3/CPPM

#### J-P Cachemiche, CPP Marseille

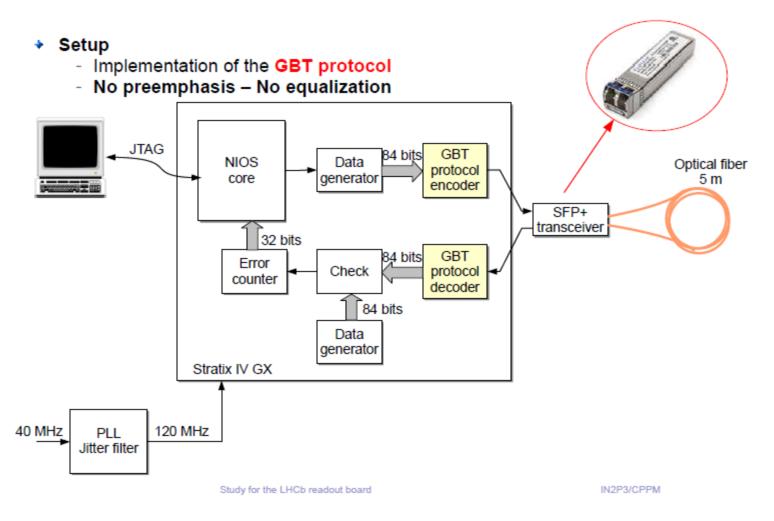

# Serial I/O

## Serial lines at 8 Gbits/s

#### J-P Cachemiche, CPP Marseille

# Serial I/O

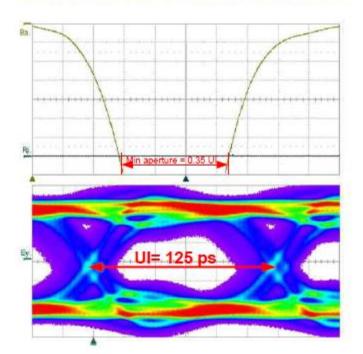

#### Measurements at 8 Gbits/s

Serial link at 8 Gbits/s with GBT protocol

- Measured jitter at 10<sup>-12</sup> Total : 77 ps (p to p) Random : 3.0 ps Deterministic : 36 ps

- Estimated error rate : 10<sup>-15</sup> without pre-emphasis or equalization

- Closure of eye diagram: inter symbol interference due to attenuation of high frequencies

Study for the LHCb readout board

IN2P3/CPPM

#### J-P Cachemiche, CPP Marseille

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

# Full $\mu$ TCA prototype

## **µTCA** Prototype

#### J-P Cachemiche, CPP Marseille

#### Jean-Francois Genat, LPNHE Paris, October 24th 2010

# xTCA CPP Marseille

## Conclusions

- Study on signal integrity is on-going

- Serial links at 4.8 and 8.5 Gbits/s are OK

- Pre-emphasis and equalization should allow to increase speed up to 10 Gigabit/s

- New version of the board with Stratix GT running at 10 Gbits/s soon available.

- xTCA system can be used to build scalable architectures for LHCb upgrade

- Advantages of a standard: mechanics, COTS systems, interoperability, ...

- Star topologies present in the standard might help for time distribution, slow control and communications between boards.

- Mezzanine concept allows flexible reconfiguration of boards

- Quick redesign at low cost

- Supervision system based on NIOS cores embedded in FPGAs is very promizing

Study for the LHCb readout board

#### J-P Cachemiche, CPP Marseille

# A demonstrator for a level-1 trigger system based on µTCA technology and 5Gb/s optical links.

**Greg Iles**

Rob Frazier, Dave Newbold (Bristol University) Costas Foudas\*, Geoff Hall, Jad Marrouche, Andrew Rose (Imperial College)

20 September 2010

\* Recently moved to University Ioannina

# New Interconnect Technologies

# CCDs, Pixels

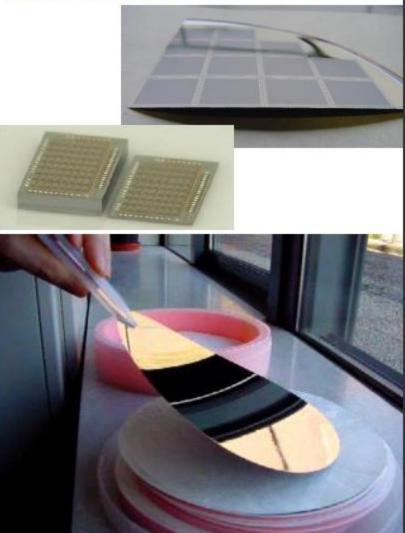

## BACKSIDE ILLUMINATED IMAGERS: THINNING

- Technology:

- Course + fine grinding

- Critical: thinning damage, impact on devices

- Wafer handling:

- Very thin wafers (< 100 um): use of carrier wafers and temporary wafer (de-)bonding technology

- IMEC results:

- Thinning down to 15 um

- Total thickness variation ~ 2 um on 200 mm wafer

imec

© IMEC 2010 PIET DE MOOR

#### Jean-Francois Genat, LPNHE Paris, October 24th 2010

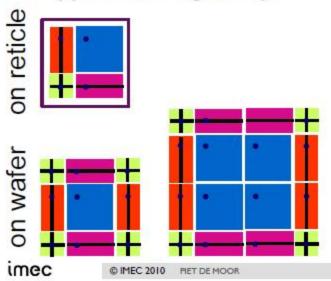

## CCDs, Pixels

## LARGE AREA IMAGERS: STITCHING

- Stitching allows large area imagers:

- Up to I imager per wafer

- Different imager sizes on one wafer demonstrated:

- I2xI2 mm<sup>2</sup>, 25x25 mm<sup>2</sup> and 50x50 mm<sup>2</sup>

- Application: e.g. X-ray

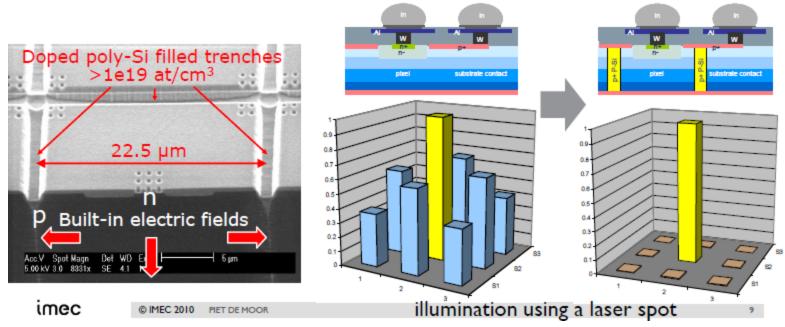

# Imagers: Pixels Insulation HYBRID BACKSIDE ILLUMINATED IMAGERS : TRENCHES FOR ZERO CROSS-TALK

- Poly-Si doped trenches separating pixels:

- Disadvantage: (limited) reduction in fill-factor

- Advantage: no cross-talk

- Demonstrated using laser point source

- ongoing optimization: recovery of good charge collection & QE/

#### Jean-Francois Genat, LPNHE Paris, October 24th 2010

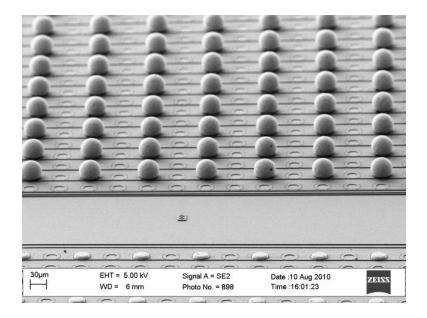

- The ultimate low-cost solder ball placement process is the mass transfer of solder spheres on the whole wafer at the same time.

- Stencil grid with predefined holes and vacuum is used to lift the solder sphere.

- Solder bumping defects can be repaired with the singe solder ball placement systems

- Limited by ball size, minimum 60 µm at present therefore suitable for 100 mm pitch

- Pac Tech foresees 40 µm bumps coming in 1-2 years.

Solder mass transfer is very efficient process to attach the solder spheres to wafer

## **Bump-bonding**

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

Sami Vaehaenen (CERN)

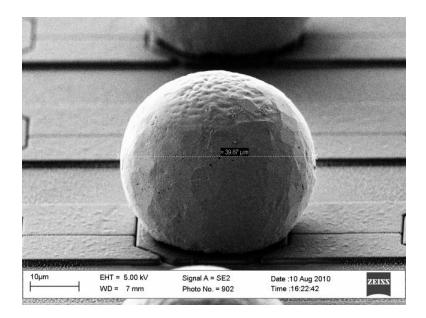

# Solder Ball Placement Test

- 40 μm sized solder balls (very advanced) were jetted (spitting process) on a Timepix chips with ENEPIG UBM with 110 μm pitch at Pac Tech.

- Individual shear tests were done (30 bumps), giving an average shear force of 8 grams / bump (good results).

- Looking forward to do more SBB tests on Timepix chips

#### Sami Vaehaenen (CERN)

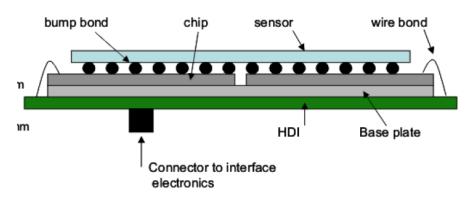

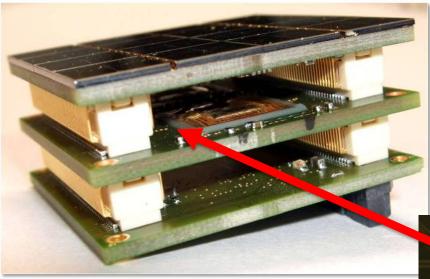

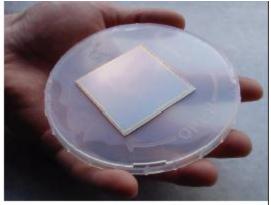

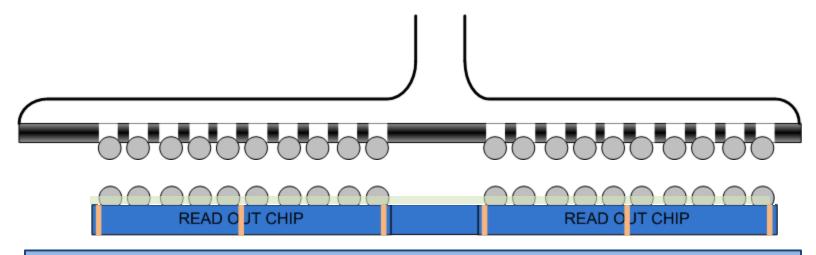

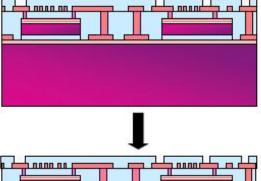

## **AREA 3D INTEGRATED IMAGERS**

- Status: system architecture study of an imaging system on a chip-stack

- Integration of micro-optics layer:

- Ultra wide field of view

- Filters for hyperspectral imaging

- Shared pixels = multiple pixels per bump

- Smart analog/digital read-out:

- Ultra high dynamic range

- ADC per group of pixels

- Variable resolution (active binning)

- Smart digital processing:

- 2D distributed group of processors

- Face recognition

- Next step: demonstrator design and manufacturing

imec

© IMEC 2010 PIET DE MOOR

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

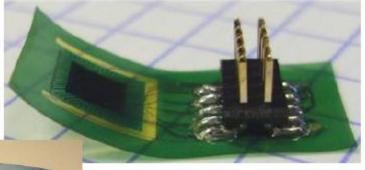

## ADVANCED INTEGRATION: FLEX EMBEDDED IMAGER

Technology:

ongoing

- Extreme wafer thinning (20 um)

- Embedding on flex

- Example of related IMEC techno:

- Functional microcontroller in flex substrate

- Embedding of tracking imager

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

## CONCLUSIONS

- Advanced 3D integration technology enables smart imagers with high performance

- The best integration scheme is application dependent

- imec has capabilities in:

- Backside thinning and passivation

- High density bumps

- Through Si vias

- Advanced assembly

- imec can offer specialty product development on demand up to small volume production (CMORE)

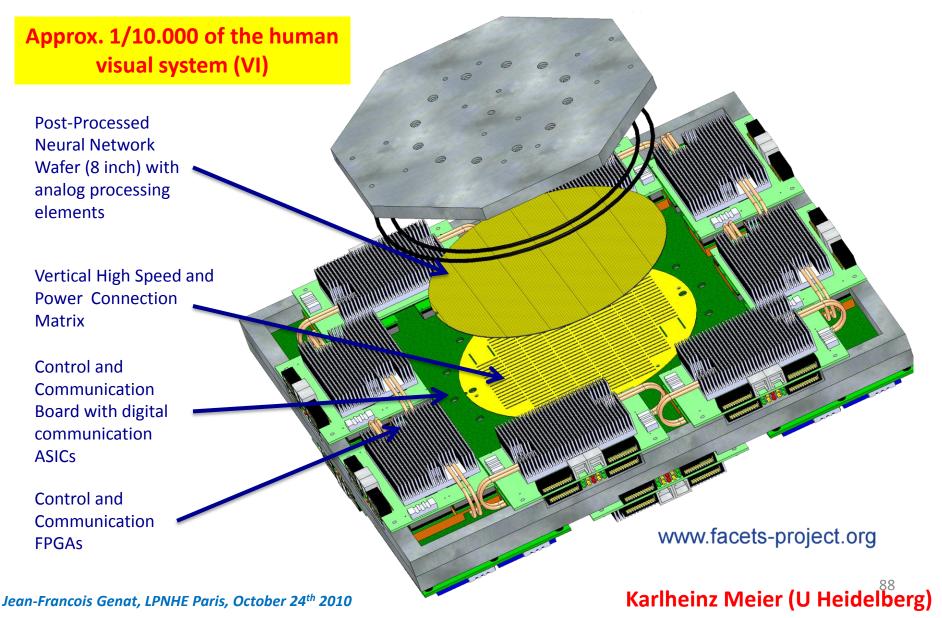

# **Parallel Computing**

Neural Processing Unit, 200.000 Neurons, 50.000.000 Synapses Demonstrate self-organized, fault tolerant, low power, accelerated information processing (Heidelberg, BrainScales Consortium))

#### Karlheinz Meier (U Heidelberg)

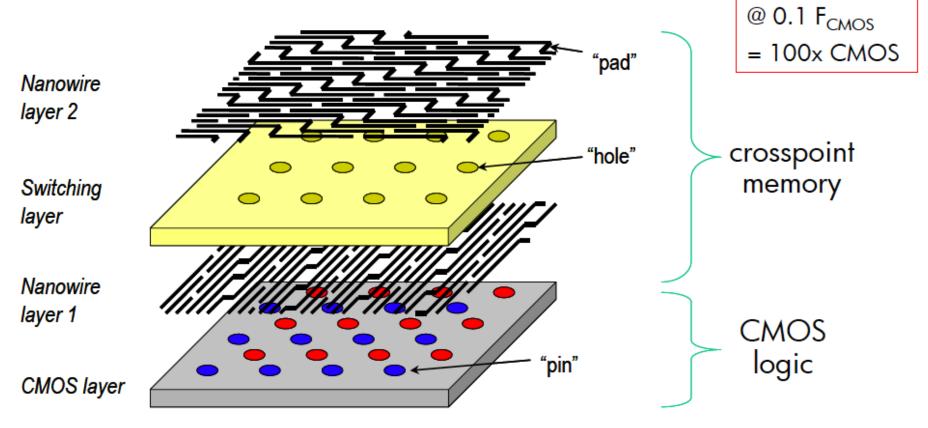

#### HP FPNI : Field Programmable Nanowire Interconnect

Nano redundancy → defect tolerance Small size, high yield → low cost Low energy

## G. Snider et al, IEEE Trans. Nano (2007)

Joining reliable CMOS and faulty nanoelectronics

Jean-Francois Genat, LPNHE Paris, October 24th 2010

# **Radiation Hardness**

## **Radiation Hardening for Space Applications**

- Dedicated processes for space are not affordable any more

- SOI is sometimes used

- ▲ Low SEU rates, latch-up free, some concerns on TID

- SOI is less readily available, analogue IPs need to be re-developed

- Total Ionising Dose (TID)

- Most space missions are limited to 100 krad dose, and in 180 nm or below, TID protection might be limited to e.g. screening of (commercial) library cells, elimination of certain transistor types

- Some long duration, deep space missions are in the Mrad domain, requiring mitigation e.g. by special transistor geometries (ELT), guard rings or derating

- Single Event Latch-Up (SEL)

- A Horizontal: mitigation in layout, e.g. guard rings

- Vertical: thickness of the epitaxial layer, deep n-well

- Single Event Effects (SEE) by Transient and Upset (SET, SEU)

- A Spatial or temporal redundancy

- $\wedge$  Mitigation by design of library cells or in logic design  $\rightarrow$  see below

#### **Roland Weigand (ESA)**

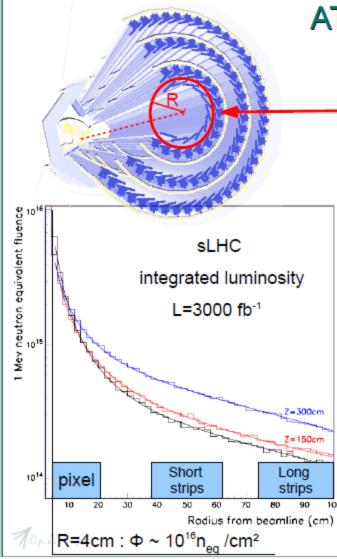

# ATLAS Silicon detectors upgrade

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

# Design and Performance of Single-Sided Modules within an Integrated Stave Assembly for the ATLAS Tracker Barrel Upgrade

Ashley Greenall The University of Liverpool

## Silicon strips !

Jean-Francois Genat, LPNHE Paris, October 24th 2010

# Silicon strips for the ATLAS upgrade

- Introduction to the Stave concept

- Stave flex hybrid

- Assembly & Electrical performance

- Stave module

- Assembly & Electrical performance

- First look at multi-module performance

- Summary and outlook

#### Jean-Francois Genat, LPNHE Paris, October 24th 2010

# Silicon strips for the ATLAS upgrade

- Have successfully demonstrated the design and build of a substrate-less module

- Issues of yield and volume production being addressed from the outset

- Individually, serially powered modules, have been shown to perform excellently

- First tests of a serially powered multi-module short stave (Stavelet) are very promising

- Stavelet tests are ongoing (with future plans for a DCDC powered variant)

- Intention is to build a module using the new shield-less hybrids (reduced material)

- Longer term, the plan is to build a full size double-sided Stave composed of 24 modules

## Pixels for the ATLAS upgrade

## ICV-SLID interconnection technology for the ATLAS pixel upgrade at SLHC

L. Andricek, <u>M. Beimforde</u>, A. Macchiolo, H.-G. Moser, R. Nisius, R.A. Richter, P. Weigell

Max-Planck-Institut für Physik, München

Jean-Francois Genat, LPNHE Paris, October 24th 2010

# ATLAS Vertex upgrade (B-Layer)

M. Beimforde: ICV-SLID for the ATLAS pixel upgrade

## **ATLAS Pixel detector Upgrades**

#### Phase 1 upgrade:

- ➔ Surpass LHC design luminosity by ~ 2016

- Insert new innermost pixel layer (b-Layer) IBL into the present one. R~3.3cm

#### Phase 2 upgrade (Super LHC):

- → Plan: (5 -10) x 10<sup>34</sup>/cm<sup>2</sup>s → (5 -10)-fold increase

- Completely new pixel detector is needed

- Pixel modules from 3.7cm < R < 20.9cm (current: 5.1cm < R < 12.2cm)</p>

- → Very compact modules needed!

- Cheap modules wanted!

- ➔ Less multiple scattering (material) desired!

#### sLHC radiation environment:

- → Integrated fluence: Φ~10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup> (scaled to damage of 1 MeV neutrons) after 3000fb<sup>-1</sup>

- ➔ Radiation damage esp. for inner pix. layers

- ➔ Radiation hard modules needed!

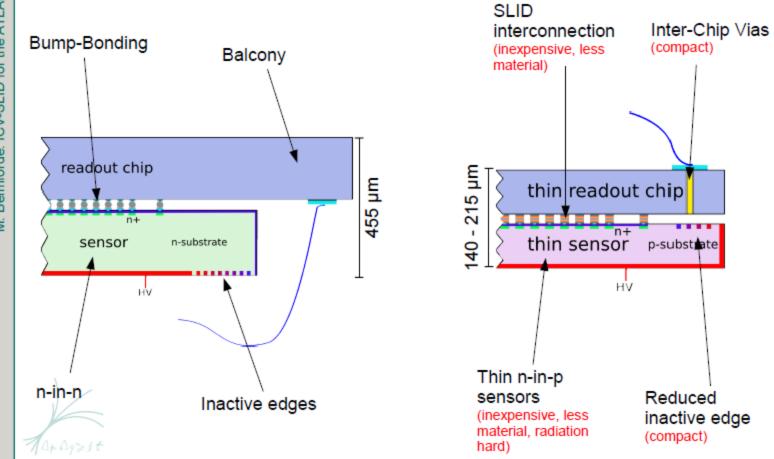

# Thin Pixel technology

## The MPP module concept

ATLAS standard

Novel MPP concept

# M. Beimforde: ICV-SLID for the ATLAS pixel upgrade

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

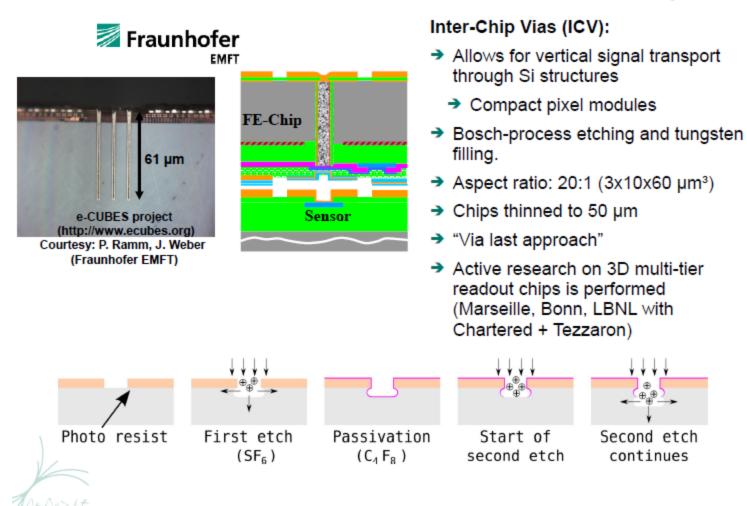

# Thin Pixel technology

## Inter-Chip Vias

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

# Triggers

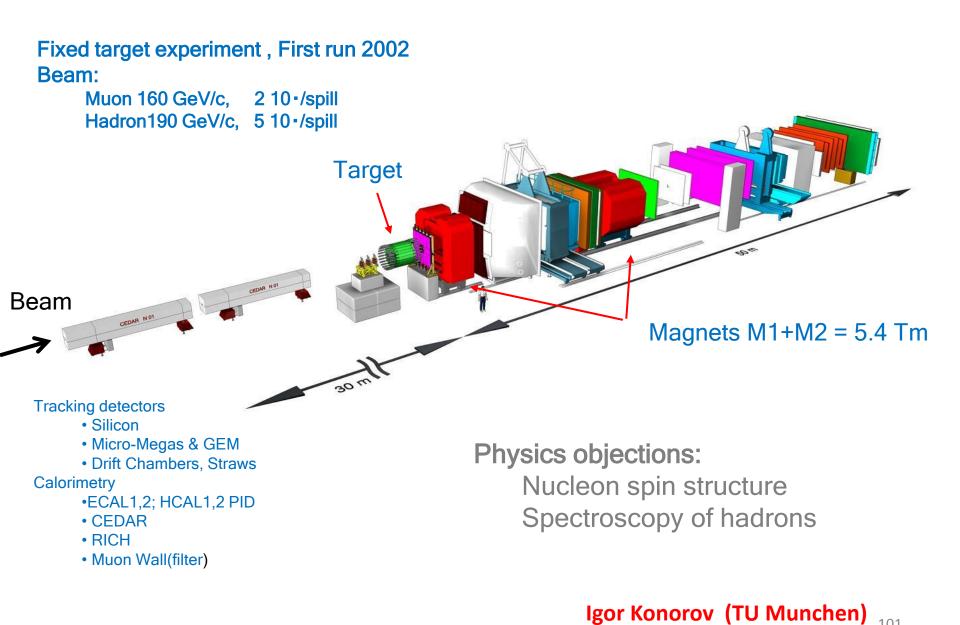

## COMPASS spectrometer @SPS CERN

101

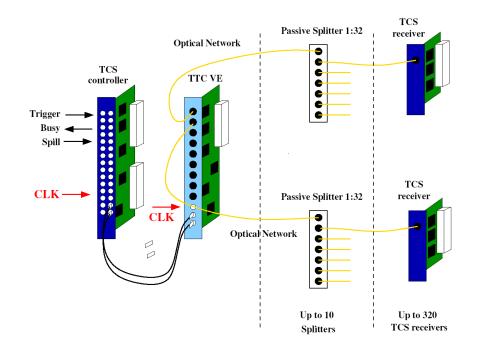

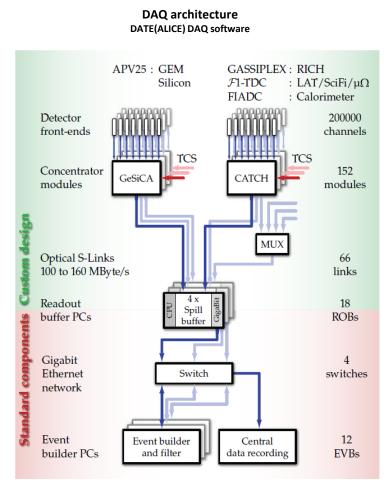

## DAQ and Trigger Distribution System

#### **Trigger Control System**

- TCS architecture derived from TTC (LHC)

- Built using commercial components

- Trigger distributed synchronously with 38.88 MHz clock

Maximum trigger rate: 30kHz

102

Igor Konorov (TU Munchen) Игорь Коноров

#### Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

# TDC based Trigger Logic in FPGA

#### Motivation:

Currently COMPASS trigger electronics is based mostly on NIM modules. Substitute NIM logic with flexible FPGA based electronics

#### What is the Trigger logic?

Interconnection of simple logical components: OR, INV, AND

#### How a Digital Trigger Logic look like:

- Synchronous pipeline architecture predictable behavior

- Convert analog Timing Information into DIGITs (TDC in FPGA)

- Unified interface : LEMO cable substitutd by FIFO like interface with TDC i

- Library components: NxOR, Nx(N)AND

#### How to create an FPGA firmware

- − Interconnections ⇔ Described in Top level VHDL file

- User creates schematic(net list)

- Software tools generate TOP level VHDL file

# Goal: provide a possibility to create a Complex Trigger Logic without a FPGA/VHDL knowledge

Игорь Коноров

#### Igor Konorov (TU Munchen)

# Trigger logic components

- TDC

- Programmable delays

- AND, OR, NAND with programmable coincidence window(GATE) and master signal

- Time calibration automatic scanning signal timing

- Monitoring

- DAQ interface no need for splitting signals to TDCs

- Inter module interface for scaling up the system

# Software

- GUI for creating trigger logic schematic

- Software for generation VHDL code and project files

- Standard Xilinx tools to be used for implementation

- No special knowledge required for using the system

#### Igor Konorov (TU Munchen)

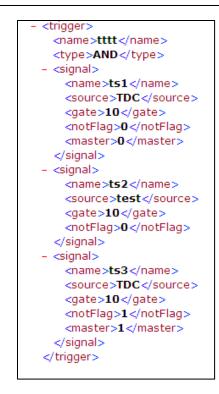

## Generation top level VHDL file

## Input:

- Template file "top\_level.vhd"

- Configuration file "trigger\_logic.xml"

## Java program generate VHDL file

- New signals declaration

- Components instantiation

```

tttt : trigger_logic

generic map (

LEVEL => 2,

SLAVE_NUMBER => 2,

DELAY_PRO_LEVEL => 10,

TRIGGER_TYPE => 0

)

port map (

control => control,

t => t,

channels_in => channels_in_tttt,

result => result_tttt

);

```

Jean-Francois Genat, LPNHE Paris, October 24<sup>th</sup> 2010

Игорь Коноров

Igor Konorov (TU Munchen)<sup>105</sup>

# LHC Status and Plans

# Physics at LHC

## To be solved by LHC !

- The goal of LHC is to complete Standard Model with Higgs boson (to complete electroweak theory)

- Would explain the particules's masses

- e<sup>-</sup>: 511 keV/c<sup>2</sup>, n/p (930 MeV/c<sup>2</sup>), μ (105 MeV/c<sup>2</sup>), τ (1785 MeV/c<sup>2</sup>), Z (91 GeV/c<sup>2</sup>), W (80 GeV/c<sup>2</sup>)

- Should be light (less than 200 GeV) following LEP/SLD

- Golden mode at LHC is  $H \rightarrow \gamma \gamma$

- A lot of expectations in EM calorimeters !

- Other modes have a lot of background, may be not easily under control (strong force)

HEP for pedestrians - TWEPP 2010

#### Patrick Puzo (LAL Orsay)

# Physics at LHC/ILC needs...

## From detector point of view

- Very demanding on:

- hermiticity to improve E<sub>T</sub> measurement

- detector quality (no dead channels)

- Higher granularity requires lower consumption

- From ATLAS LAr FEB electronics (1W/ch) to ILC needs (100  $\mu W/ch)$

Patrick Puzo (LAL Orsay)

HEP for pedestrians - TWEPP 2010

# LHC Getting to Nominal (Dates Indicative)

| 2010          | 2011                     | 2012                        | 2013                               | 2015 | 2016 |  |  |  |  |  |  |

|---------------|--------------------------|-----------------------------|------------------------------------|------|------|--|--|--|--|--|--|

| Energy 3.5TeV |                          | g                           | Increase Beam Energy to 7TeV       |      |      |  |  |  |  |  |  |

| β* <b>c</b>   | f 2m                     | Splices, Collimators in IR3 | Decrease<br>β* to<br>0.55m         |      |      |  |  |  |  |  |  |

|               | 0%<br>I <sub>nom</sub>   |                             | Increase k <sub>b</sub><br>to 2808 |      |      |  |  |  |  |  |  |

| 2 1           | tial<br>10 <sup>32</sup> |                             | Nominal<br>10 <sup>34</sup>        |      |      |  |  |  |  |  |  |

| 1             | fb <sup>-1</sup>         |                             | ≤ 50 fb <sup>-1</sup> /yr          |      |      |  |  |  |  |  |  |

#### Ralph Assmann (CERN)

# LHC Overall Strategy >2016 (Dates Indicative)

| 2017 | 2018           | 2019                | 2020 | 2021                                                       | 2022 | 2023 | 2024 | 2025  | 2026                | 2027 | 2028                                | 2029 | 2030 | 2031 | 2032 | 2033          | 2034               | 2035 | etc. |

|------|----------------|---------------------|------|------------------------------------------------------------|------|------|------|-------|---------------------|------|-------------------------------------|------|------|------|------|---------------|--------------------|------|------|

|      |                |                     | _    |                                                            |      |      |      |       |                     |      | Increase Beam Energy<br>to 16.5 TeV |      |      |      |      |               |                    |      |      |

|      |                |                     |      | New interaction region<br>(β*to 0.2m, luminosity leveling) |      |      |      |       |                     |      |                                     |      |      |      |      |               |                    |      |      |

|      | creas<br>brigh |                     |      |                                                            |      |      |      |       |                     |      |                                     |      |      |      |      |               |                    |      |      |

|      | Ultir          | nate                |      |                                                            |      |      |      | HL-I  | LHC                 |      |                                     |      |      |      |      | HE-           | LHC                |      |      |

|      | 2.3            |                     |      | 5 10 <sup>34</sup>                                         |      |      |      |       |                     |      | <b>2</b> 10 <sup>34</sup>           |      |      |      |      |               |                    |      |      |

| -    | ≤ 100          | fb <sup>-1</sup> /y | /r   |                                                            |      |      | 5    | ≤ 200 | fb <sup>-1</sup> /y | /r   |                                     |      |      |      | 5    | ≦ <b>10</b> 0 | fb <sup>-1</sup> / | yr   |      |

#### Ralph Assmann (CERN)

(Astérix et les Goths. Texte René Goscinny, Dessins Albert Uderzo, Editeur Hachette)

2035...

# Thanks !!!